参数资料

| 型号: | XA3SD1800A-4FGG676I |

| 厂商: | Xilinx Inc |

| 文件页数: | 30/58页 |

| 文件大小: | 0K |

| 描述: | SPARTAN-3ADSP FPGA 1800K 676FBGA |

| 产品培训模块: | Extended Spartan 3A FPGA Family |

| 标准包装: | 40 |

| 系列: | Spartan®-3A DSP XA |

| LAB/CLB数: | 4160 |

| 逻辑元件/单元数: | 37440 |

| RAM 位总计: | 1548288 |

| 输入/输出数: | 519 |

| 门数: | 1800000 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 676-BGA |

| 供应商设备封装: | 676-FBGA(27x27) |

| 配用: | 122-1574-ND - KIT DEVELOPMENT SPARTAN 3ADSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

XA Spartan-3A DSP Automotive FPGA Family Data Sheet

DS705 (v2.0) April 18, 2011

Product Specification

36

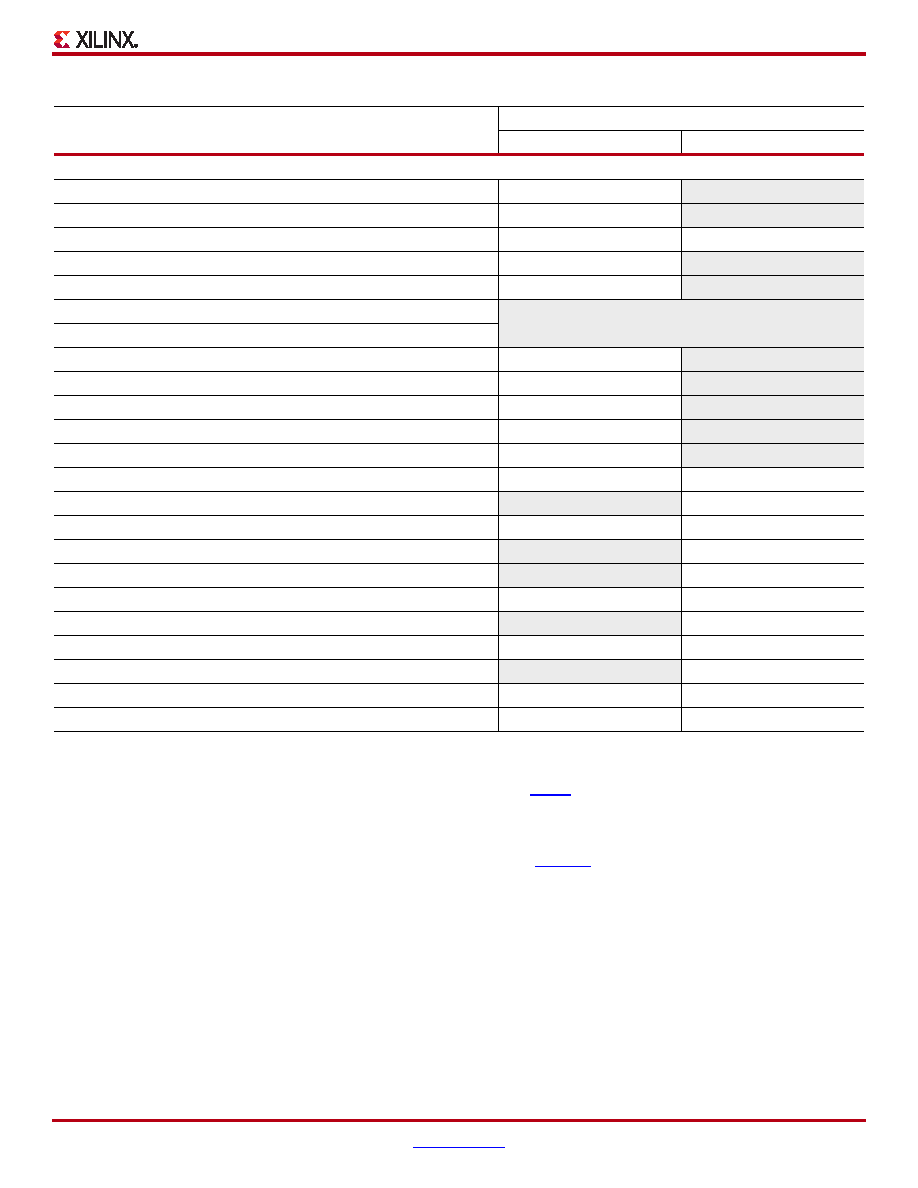

Differential Standards (Number of I/O Pairs or Channels)

LVDS_25

22

–

LVDS_33

27

–

BLVDS_25

44

MINI_LVDS_25

22

–

MINI_LVDS_33

27

–

LVPECL_25

Inputs Only

LVPECL_33

RSDS_25

22

–

RSDS_33

27

–

TMDS_33

27

–

PPDS_25

22

–

PPDS_33

27

–

DIFF_HSTL_I_18

8

DIFF_HSTL_II_18

–2

DIFF_HSTL_III_18

5

4

DIFF_HSTL_I

–10

DIFF_HSTL_III

–4

DIFF_SSTL18_I

3

7

DIFF_SSTL18_II

–1

DIFF_SSTL2_I

99

DIFF_SSTL2_II

–4

DIFF_SSTL3_I

45

DIFF_SSTL3_II

33

Notes:

1.

Not all I/O standards are supported on all I/O banks. The left and right banks (I/O banks 1 and 3) support higher output drive current than

the top and bottom banks (I/O banks 0 and 2). Similarly, true differential output standards, such as LVDS, RSDS, PPDS, miniLVDS, and

TMDS, are only supported in top or bottom banks (I/O banks 0 and 2). Refer to UG331, Spartan-3 Generation FPGA User Guide for

additional information.

2.

The numbers in this table are recommendations that assume sound board layout practice. This table assumes the following parasitic factors:

combined PCB trace and land inductance per VCCO and GND pin of 1.0 nH, receiver capacitive load of 15 pF. Test limits are the VIL/VIH

voltage limits for the respective I/O standard.

3.

If more than one signal standard is assigned to the I/Os of a given bank, refer to XAPP689, Managing Ground Bounce in Large FPGAs for

information on how to perform weighted average SSO calculations.

Table 29: Recommended Number of Simultaneously Switching Outputs per VCCO/GND Pair (VCCAUX=3.3V) (Cont’d)

Signal Standard (IOSTANDARD)

Package Type: CSG484 and FGG676

Top, Bottom (Banks 0,2)

Left, Right (Banks 1,3)

相关PDF资料 |

PDF描述 |

|---|---|

| SST25VF020B-80-4I-QAE | IC FLASH SER 2MB 80MHZ SPI 8WSON |

| XC6SLX75T-3FGG676C | IC FPGA SPARTAN 6 74K 676FGGBGA |

| 24AA256T-I/SM | IC EEPROM 256KBIT 400KHZ 8SOIC |

| XC6SLX100-N3FGG676I | IC FPGA SPARTAN-6 676FBGA |

| 25C160T-E/SN | IC EEPROM 16KBIT 3MHZ 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XA3SD1800A-4FGG676Q | 功能描述:SPARTAN-3ADSP FPGA 1800K 676FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A DSP XA 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XA3SD3400A | 制造商:XILINX 制造商全称:XILINX 功能描述:XA Spartan-3A DSP Automotive FPGA Family Data Sheet |

| XA3SD3400A-4CSG484I | 功能描述:SPARTAN-3ADSP FPGA 3400K 484CSBG RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A DSP XA 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XA3SD3400A-4FGG676I | 功能描述:SPARTAN-3ADSP FPGA 3400K 676FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A DSP XA 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| X-A4A-300L | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

发布紧急采购,3分钟左右您将得到回复。