- 您现在的位置:买卖IC网 > PDF目录19837 > XC2C32A-6QFG32C (Xilinx Inc)IC CRII CPLD 32MCRCELL 32QFN PDF资料下载

参数资料

| 型号: | XC2C32A-6QFG32C |

| 厂商: | Xilinx Inc |

| 文件页数: | 10/16页 |

| 文件大小: | 0K |

| 描述: | IC CRII CPLD 32MCRCELL 32QFN |

| 标准包装: | 490 |

| 系列: | CoolRunner II |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 5.5ns |

| 电压电源 - 内部: | 1.7 V ~ 1.9 V |

| 逻辑元件/逻辑块数目: | 2 |

| 宏单元数: | 32 |

| 门数: | 750 |

| 输入/输出数: | 21 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 供应商设备封装: | 32-QFN 裸露焊盘(5x5) |

| 包装: | 托盘 |

| 产品目录页面: | 600 (CN2011-ZH PDF) |

| 其它名称: | 122-1412 |

CoolRunner-II CPLD Family

DS090 (v3.1) September 11, 2008

3

Product Specification

R

CoolRunner-II CPLD I/O standards.)

Architecture Description

CoolRunner-II CPLD is a highly uniform family of fast, low

power CPLDs. The underlying architecture is a traditional

CPLD architecture combining macrocells into Function

Blocks (FBs) interconnected with a global routing matrix,

the Xilinx Advanced Interconnect Matrix (AIM). The FBs use

a Programmable Logic Array (PLA) configuration which

allows all product terms to be routed and shared among any

of the macrocells of the FB. Design software can efficiently

synthesize and optimize logic that is subsequently fit to the

FBs and connected with the ability to utilize a very high per-

centage of device resources. Design changes are easily

and automatically managed by the software, which exploits

the 100% routability of the Programmable Logic Array within

each FB. This extremely robust building block delivers the

industry’s highest pinout retention, under very broad design

conditions. The architecture is explained in more detail with

the discussion of the underlying FBs, logic and intercon-

nect.

The design software automatically manages these device

resources so that users can express their designs using

completely generic constructs without knowledge of these

architectural details. More advanced users can take advan-

tage of these details to more thoroughly understand the

software’s choices and direct its results.

Figure 1 shows the high-level architecture whereby FBs

attach to pins and interconnect to each other within the

internal interconnect matrix. Each FB contains 16 macro-

cells. The BSC path is the JTAG Boundary Scan Control

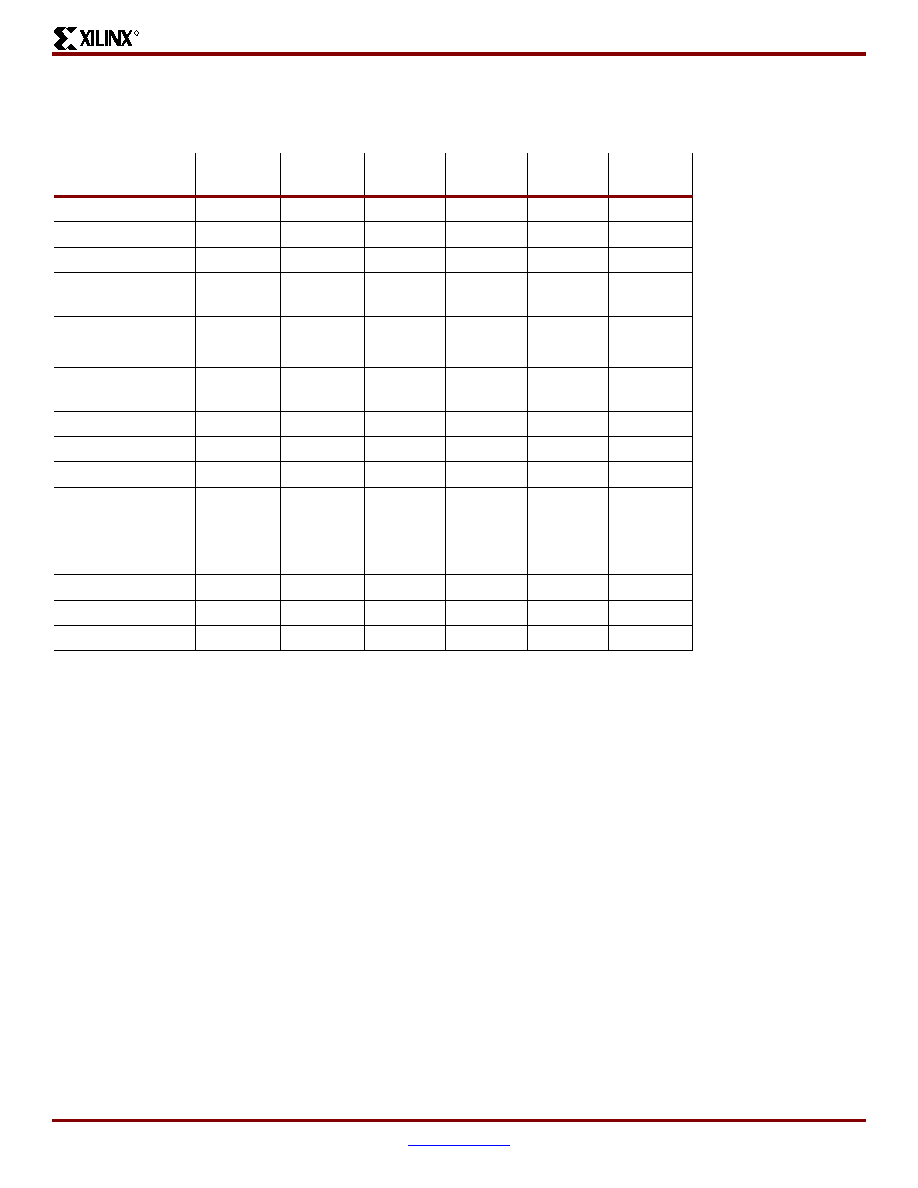

Table 4: CoolRunner-II CPLD Family Features

XC2C32A

XC2C64A

XC2C128

XC2C256

XC2C384

XC2C512

IEEE 1532

I/O banks

2

4

Clock division

-

DualEDGE

Registers

DataGATE

-

LVTTL

LVCMOS33, 25,

18, and 15(1)

SSTL2_1

-

SSTL3_1

-

HSTL_1

-

Configurable

ground

Quadruple data

security

Open drain outputs

Hot plugging

Schmitt Inputs

1.

LVCMOS15 requires the use of Schmitt-trigger inputs.

相关PDF资料 |

PDF描述 |

|---|---|

| LCMXO640C-4MN100I | IC PLD 640LUTS 74I/O 100-BGA |

| VI-2WY-CW-F2 | CONVERTER MOD DC/DC 3.3V 66W |

| VI-27W-CY-F2 | CONVERTER MOD DC/DC 5.5V 50W |

| ABM31DTBD | CONN EDGECARD 62POS R/A .156 SLD |

| EPM9560RC240-15 | IC MAX 9000 CPLD 560 240-RQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2C32A-6QFG32I | 功能描述:IC CR-II CPLD 32MCELL 32-QFN RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XC2C32A-6VQ44C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 750 GATES 32 MCRCLLS 300MHZ 0.18UM 1.8V 4 - Trays 制造商:Xilinx 功能描述:IC CPLD 32MC 5.5NS 44VQFP 制造商:Xilinx 功能描述:IC CR-II CPLD 32MCELL 44-VQFP |

| XC2C32A-6VQ44I | 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 750 GATES 32 MCRCLLS 300MHZ 0.18UM 1.8V 4 - Trays 制造商:Xilinx 功能描述:IC CPLD 32MC 5.5NS 44VQFP 制造商:Xilinx 功能描述:IC CR-II CPLD 32MCELL 44-VQFP |

| XC2C32A-6VQG44C | 功能描述:IC CR-II CPLD 32MCELL 44-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:160 系列:ispMACH® 4000V 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.5ns 电压电源 - 内部:3 V ~ 3.6 V 逻辑元件/逻辑块数目:2 宏单元数:32 门数:- 输入/输出数:30 工作温度:-40°C ~ 130°C 安装类型:表面贴装 封装/外壳:44-TQFP 供应商设备封装:44-TQFP(10x10) 包装:托盘 |

| XC2C32A-6VQG44I | 功能描述:IC CR-II CPLD 32MCELL 44-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:90 系列:ispMACH® 4A 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.5ns 电压电源 - 内部:4.75 V ~ 5.25 V 逻辑元件/逻辑块数目:- 宏单元数:64 门数:- 输入/输出数:48 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。