参数资料

| 型号: | XC2S30-5PQ208C |

| 厂商: | Xilinx Inc |

| 文件页数: | 89/99页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 2.5V 216 CLB'S 208-PQFP |

| 标准包装: | 24 |

| 系列: | Spartan®-II |

| LAB/CLB数: | 216 |

| 逻辑元件/单元数: | 972 |

| RAM 位总计: | 24576 |

| 输入/输出数: | 140 |

| 门数: | 30000 |

| 电源电压: | 2.375 V ~ 2.625 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

| 其它名称: | 122-1220 XC2S30-5PQ208C-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页当前第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

9

R

drivers are disabled. Maintaining a valid logic level in this

way helps eliminate bus chatter.

Because the weak-keeper circuit uses the IOB input buffer

to monitor the input level, an appropriate VREF voltage must

be provided if the signaling standard requires one. The

provision of this voltage must comply with the I/O banking

rules.

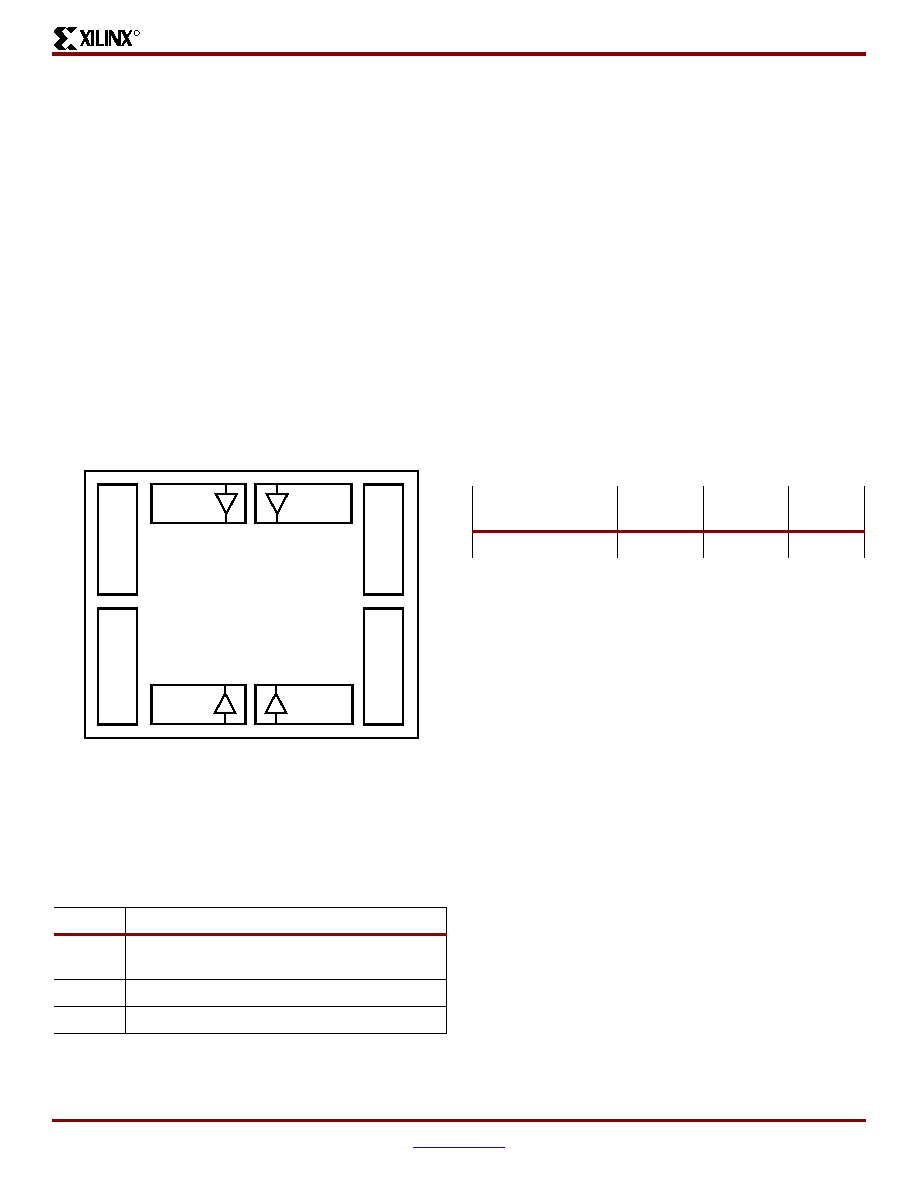

I/O Banking

Some of the I/O standards described above require VCCO

and/or VREF voltages. These voltages are externally

connected to device pins that serve groups of IOBs, called

banks. Consequently, restrictions exist about which I/O

standards can be combined within a given bank.

Eight I/O banks result from separating each edge of the

FPGA into two banks (see Figure 3). Each bank has

multiple VCCO pins which must be connected to the same

voltage. Voltage is determined by the output standards in

use.

Within a bank, output standards may be mixed only if they

use the same VCCO. Compatible standards are shown in

Table 4. GTL and GTL+ appear under all voltages because

their open-drain outputs do not depend on VCCO.

Some input standards require a user-supplied threshold

voltage, VREF. In this case, certain user-I/O pins are

automatically configured as inputs for the VREF voltage.

About one in six of the I/O pins in the bank assume this role.

VREF pins within a bank are interconnected internally and

consequently only one VREF voltage can be used within

each bank. All VREF pins in the bank, however, must be

connected to the external voltage source for correct

operation.

In a bank, inputs requiring VREF can be mixed with those

that do not but only one VREF voltage may be used within a

bank. Input buffers that use VREF are not 5V tolerant.

LVTTL, LVCMOS2, and PCI are 5V tolerant. The VCCO and

VREF pins for each bank appear in the device pinout tables.

Within a given package, the number of VREF and VCCO pins

can vary depending on the size of device. In larger devices,

more I/O pins convert to VREF pins. Since these are always

a superset of the VREF pins used for smaller devices, it is

possible to design a PCB that permits migration to a larger

device. All VREF pins for the largest device anticipated must

be connected to the VREF voltage, and not used for I/O.

Configurable Logic Block

The basic building block of the Spartan-II FPGA CLB is the

logic cell (LC). An LC includes a 4-input function generator,

carry logic, and storage element. Output from the function

generator in each LC drives the CLB output and the D input

of the flip-flop. Each Spartan-II FPGA CLB contains four

LCs, organized in two similar slices; a single slice is shown

in Figure 4.

In addition to the four basic LCs, the Spartan-II FPGA CLB

contains logic that combines function generators to provide

functions of five or six inputs.

Look-Up Tables

Spartan-II FPGA function generators are implemented as

4-input look-up tables (LUTs). In addition to operating as a

function generator, each LUT can provide a 16 x 1-bit

synchronous RAM. Furthermore, the two LUTs within a

slice can be combined to create a 16 x 2-bit or 32 x 1-bit

synchronous RAM, or a 16 x 1-bit dual-port synchronous

RAM.

The Spartan-II FPGA LUT can also provide a 16-bit shift

register that is ideal for capturing high-speed or burst-mode

data. This mode can also be used to store data in

applications such as Digital Signal Processing.

Figure 3: Spartan-II I/O Banks

Table 4: Compatible Output Standards

VCCO

Compatible Standards

3.3V

PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP,

GTL, GTL+

2.5V

SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+

1.5V

HSTL I, HSTL III, HSTL IV, GTL, GTL+

DS001_03_060100

Bank 0

GCLK3

GCLK2

GCLK1

GCLK0

Bank 1

Bank 5

Bank 4

Spartan-II

Device

Bank

7

Bank

6

Bank

2

Bank

3

Independent Banks Available

Package

VQ100

PQ208

CS144

TQ144

FG256

FG456

Independent Banks

1

4

8

相关PDF资料 |

PDF描述 |

|---|---|

| XC2S15-6CS144C | IC FPGA 2.5V C-TEMP 144-CSBGA |

| XC2S15-5CS144I | IC FPGA 2.5V I-TEMP 144-CSBGA |

| XC2S15-5CS144C | IC FPGA 2.5V C-TEMP 144-CSBGA |

| XC2S100-5FG456I | IC FPGA 2.5V I-TEMP 456-FBGA |

| IDT71V35761S183PFG | IC SRAM 4MBIT 183MHZ 100TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S30-5PQ208I | 功能描述:IC FPGA 2.5V I-TEMP 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-II 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC2S30-5PQG208C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S30-5PQG208I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S305TQ144C | 制造商:XILINX 功能描述:New |

| XC2S30-5TQ144C | 功能描述:IC FPGA 2.5V 216 CLB'S 144-TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-II 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。