参数资料

| 型号: | XC3190A-3PC84C |

| 厂商: | Xilinx Inc |

| 文件页数: | 24/76页 |

| 文件大小: | 0K |

| 描述: | IC LOGIC CL ARRAY 9000GAT 84PLCC |

| 产品变化通告: | XC4000XL/E, XC9500XV, XC3100A Discontinuance 12/Apr/2010 |

| 标准包装: | 1 |

| 系列: | XC3000A/L |

| LAB/CLB数: | 320 |

| RAM 位总计: | 64160 |

| 输入/输出数: | 70 |

| 门数: | 6000 |

| 电源电压: | 4.25 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 84-LCC(J 形引线) |

| 供应商设备封装: | 84-PLCC |

| 产品目录页面: | 601 (CN2011-ZH PDF) |

| 其它名称: | 122-1046 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

R

XC3000 Series Field Programmable Gate Arrays

7-32

November 9, 1998 (Version 3.1)

Notes:

1. The max limit of CCLK Low time is caused by dynamic circuitry inside the FPGA.

2. Configuration must be delayed until the INIT of all FPGAs is High.

3. At power-up, VCC must rise from 2.0 V to VCC min in less than 25 ms. If this is not possible, configuration can be delayed by

holding RESET Low until VCC has reached 4.0 V (2.5 V for the XC3000L). A very long VCC rise time of >100 ms, or a

non-monotonically rising VCC may require a >6-s High level on RESET, followed by a >6-s Low level on RESET and D/P

after VCC has reached 4.0 V (2.5 V for the XC3000L).

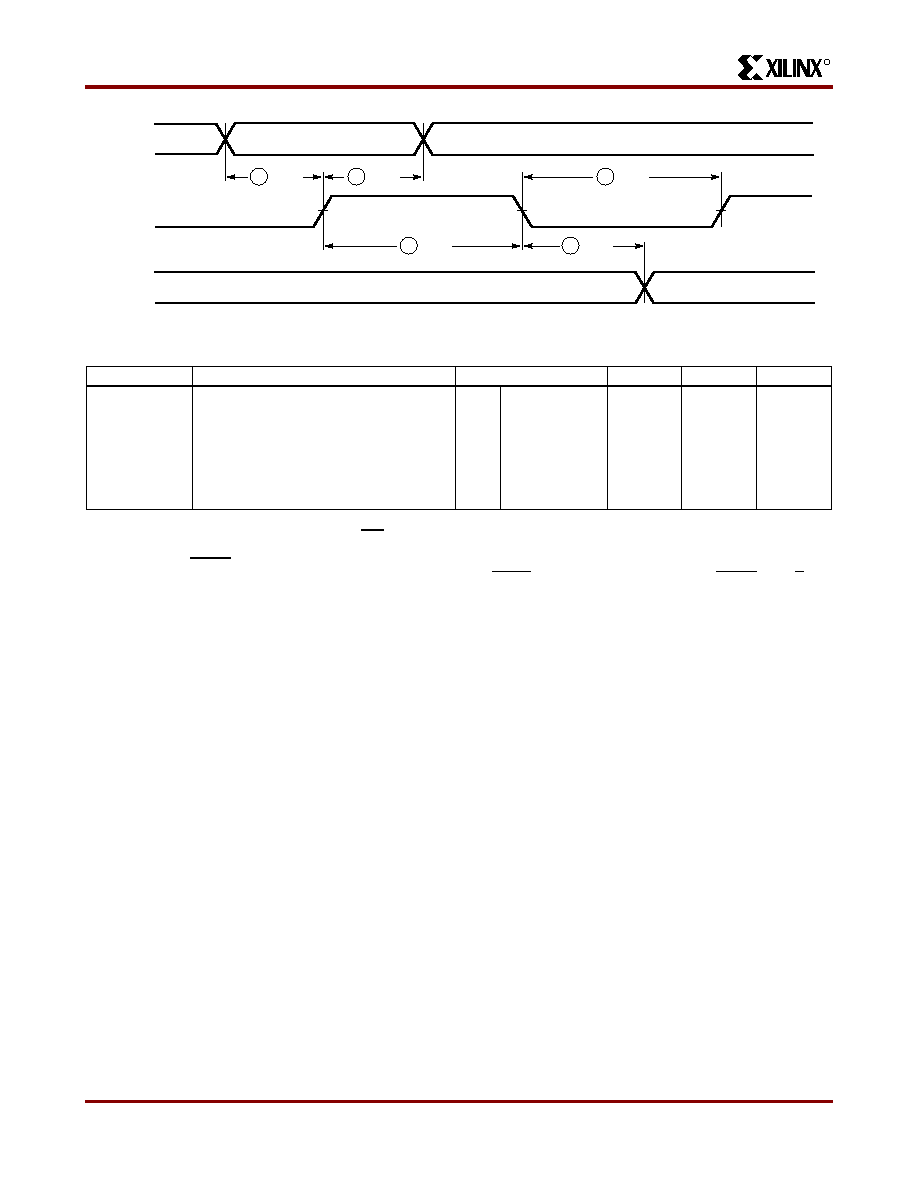

Figure 30: Slave Serial Mode Programming Switching Characteristics

4 TCCH

Bit n

Bit n + 1

Bit n

Bit n - 1

3 TCCO

5 TCCL

2 TCCD

1 TDCC

DIN

CCLK

DOUT

(Output)

X5379

Description

Symbol

Min

Max

Units

CCLK

To DOUT

DIN setup

DIN hold

High time

Low time (Note 1)

Frequency

3

1

2

4

5

TCCO

TDCC

TCCD

TCCH

TCCL

FCC

60

0

0.05

100

5.0

10

ns

s

MHz

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| ABC65DRXS | CONN EDGECARD 130PS .100 DIP SLD |

| 25LC040AX-I/ST | IC EEPROM 4KBIT 10MHZ 8TSSOP |

| 25LC040AT-I/ST | IC EEPROM 4KBIT 10MHZ 8TSSOP |

| XC3S700A-5FGG400C | IC SPARTAN-3A FPGA 700K 400FBGA |

| 25LC040AT-I/MS | IC EEPROM 4KBIT 10MHZ 8MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3190A-3PC84I | 制造商:Xilinx 功能描述: |

| XC3190A-3PG175C | 制造商:Xilinx 功能描述: |

| XC3190A-3PG175I | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3190A-3PP175C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3190A-3PP175I | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

发布紧急采购,3分钟左右您将得到回复。