参数资料

| 型号: | XC5202-6PC84C |

| 厂商: | Xilinx Inc |

| 文件页数: | 23/73页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 64 CLB'S 84-PLCC |

| 产品变化通告: | XC1700 PROMs,XC5200,HQ,SCD Parts Discontinuation 19/Jul/2010 |

| 标准包装: | 15 |

| 系列: | XC5200 |

| LAB/CLB数: | 64 |

| 逻辑元件/单元数: | 256 |

| 输入/输出数: | 65 |

| 门数: | 3000 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 84-LCC(J 形引线) |

| 供应商设备封装: | 84-PLCC |

| 其它名称: | 122-1131 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

R

November 5, 1998 (Version 5.2)

7-85

XC5200 Series Field Programmable Gate Arrays

7

XC3000 family: XC5200 devices support an additional pro-

gramming mode: Peripheral Synchronous.

XC3000 family: The XC5200 family does not support

Power-down, but offers a Global 3-state input that does not

reset any flip-flops.

XC3000 family: The XC5200 family does not provide an

on-chip crystal oscillator amplifier, but it does provide an

internal oscillator from which a variety of frequencies up to

12 MHz are available.

Architectural Overview

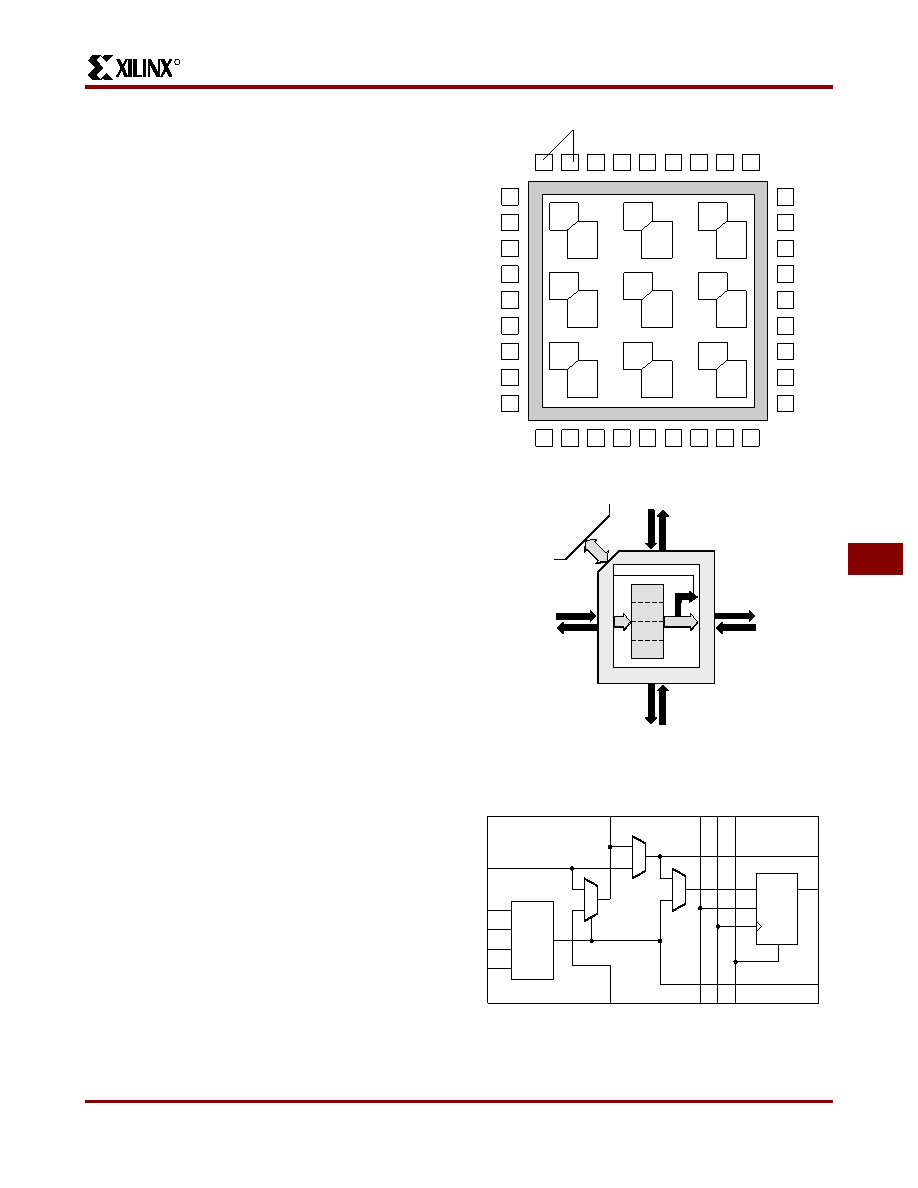

Figure 1 presents a simplified, conceptual overview of the

XC5200 architecture. Similar to conventional FPGAs, the

XC5200 family consists of programmable IOBs, program-

mable logic blocks, and programmable interconnect. Unlike

other FPGAs, however, the logic and local routing

resources of the XC5200 family are combined in flexible

VersaBlocks (Figure 2). General-purpose routing connects

to the VersaBlock through the General Routing Matrix

(GRM).

VersaBlock: Abundant Local Routing Plus

Versatile Logic

The basic logic element in each VersaBlock structure is the

Logic Cell, shown in Figure 3. Each LC contains a 4-input

function generator (F), a storage device (FD), and control

logic. There are five independent inputs and three outputs

to each LC. The independence of the inputs and outputs

allows the software to maximize the resource utilization

within each LC. Each Logic Cell also contains a direct

feedthrough path that does not sacrifice the use of either

the function generator or the register; this feature is a first

for FPGAs. The storage device is configurable as either a D

flip-flop or a latch. The control logic consists of carry logic

for fast implementation of arithmetic functions, which can

also be configured as a cascade chain allowing decode of

very wide input functions.

Figure 1: XC5200 Architectural Overview

Figure 2: VersaBlock

Figure 3: XC5200 Logic Cell (Four LCs per CLB)

X4955

GRM

Input/Output Blocks (IOBs)

Versa-

Block

GRM

Versa-

Block

VersaRing

GRM

Versa-

Block

GRM

Versa-

Block

GRM

Versa-

Block

GRM

Versa-

Block

GRM

Versa-

Block

GRM

Versa-

Block

GRM

Versa-

Block

VersaRing

X5707

CLB

Direct Connects

TS

GRM

LIM

4

LC3

LC2

LC1

LC0

4

44

24

X4956

F4

F3

F

FD

F2

F1

DQ

X

DO

DI

CO

CI

CE CK

CLR

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| FMC31DRXH | CONN EDGECARD 62POS DIP .100 SLD |

| XC4036XL-2HQ240C | IC FPGA 1296 CLB'S 240-HQFP |

| ABB60DHAS-S793 | CONN EDGECARD 120POS R/A .05 REV |

| IDT71V424S12YG | IC SRAM 4MBIT 12NS 36SOJ |

| FMM24DSEI-S13 | CONN EDGECARD 48POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5202-6PC84I | 制造商:Xilinx 功能描述: |

| XC5202-6PG156C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5202-6PG191C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5202-6PG223C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5202-6PG299C | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。