- 您现在的位置:买卖IC网 > PDF目录19298 > XC5VLX110-3FFG1760C (Xilinx Inc)IC FPGA VIRTEX-5 110K 1760FBGA PDF资料下载

参数资料

| 型号: | XC5VLX110-3FFG1760C |

| 厂商: | Xilinx Inc |

| 文件页数: | 47/91页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX-5 110K 1760FBGA |

| 标准包装: | 1 |

| 系列: | Virtex®-5 LX |

| LAB/CLB数: | 8640 |

| 逻辑元件/单元数: | 110592 |

| RAM 位总计: | 4718592 |

| 输入/输出数: | 800 |

| 电源电压: | 0.95 V ~ 1.05 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 1760-BBGA,FCBGA |

| 供应商设备封装: | 1760-FCBGA |

| 配用: | 568-5088-ND - BOARD DEMO DAC1408D750 HW-V5-ML523-UNI-G-ND - EVALUATION PLATFORM VIRTEX-5 HW-AFX-FF1760-500-G-ND - BOARD DEV VIRTEX 5 FF1760 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页当前第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页

Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

DS202 (v5.3) May 5, 2010

Product Specification

51

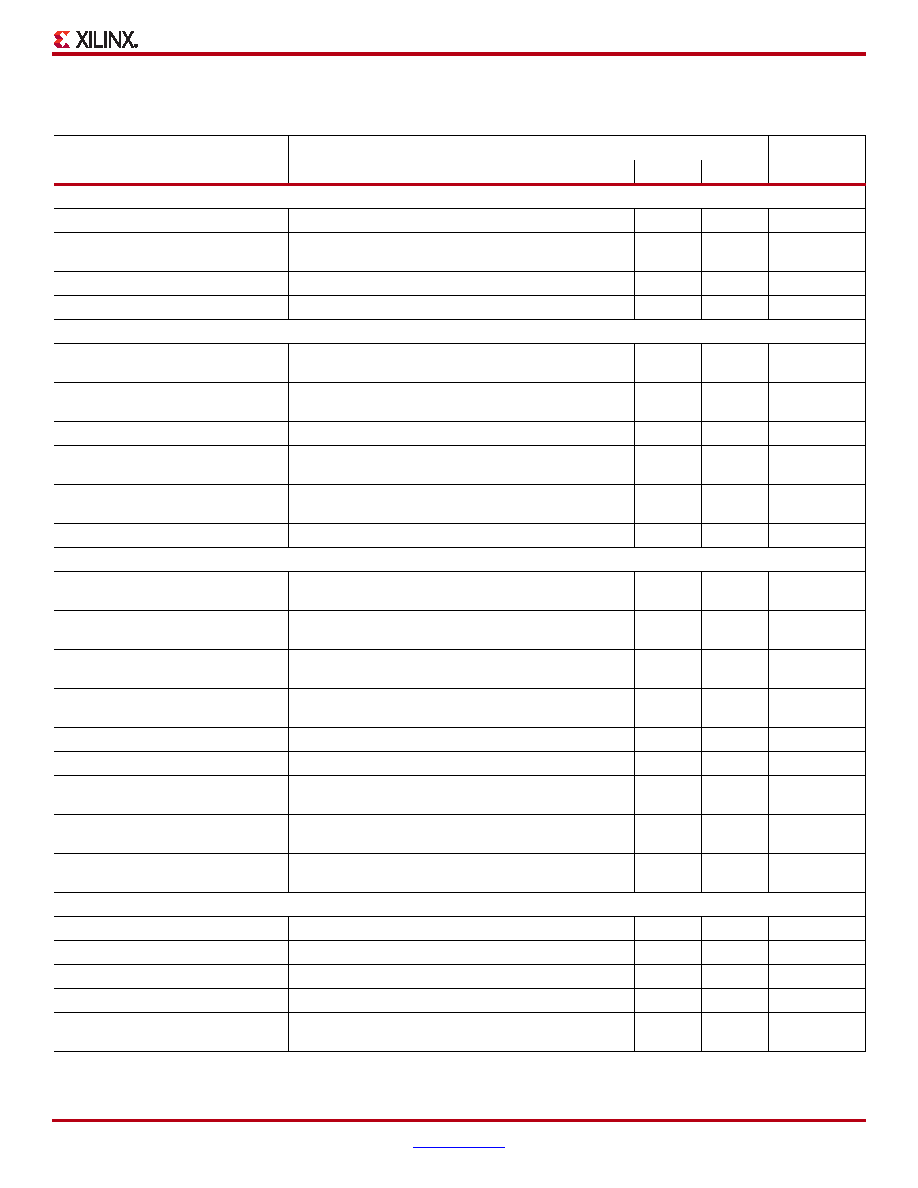

Configuration Switching Characteristics

Table 70: Configuration Switching Characteristics

Symbol

Description

Speed Grade

Units

-3

-2

-1

Power-up Timing Characteristics

TPL

Program Latency

3

ms, Max

TPOR

Power-on-Reset

10

50

10

50

10

50

ms, Min/Max

TICCK

CCLK (output) delay

400

ns, Min

TPROGRAM

Program Pulse Width

250

ns, Min

Master/Slave Serial Mode Programming Switching(1)

TDCCK/TCCKD

DIN Setup/Hold, slave mode

4.0

0.0

4.0

0.0

4.0

0.0

ns, Min

TDSCCK/TSCCKD

DIN Setup/Hold, master mode

4.0

0.0

4.0

0.0

4.0

0.0

ns, Min

TCCO

DOUT

7.5

ns, Max

FMCCK

Maximum Frequency, master mode with

respect to nominal CCLK.

100

MHz,

Max

FMCCKTOL

Frequency Tolerance, master mode with

respect to nominal CCLK.

±50

%

FMSCCK

Slave mode external CCLK

100

MHz

SelectMAP Mode Programming Switching(1)

TSMDCCK/TSMCCKD

SelectMAP Data Setup/Hold

3.0

0.5

3.0

0.5

3.0

0.5

ns, Min

TSMCSCCK/TSMCCKCS

CS_B Setup/Hold

3.0

0.5

3.0

0.5

3.0

0.5

ns, Min

TSMCCKW/TSMWCCK

RDWR_B Setup/Hold

8.0

0.5

8.0

0.5

8.0

0.5

ns, Min

TSMCKCSO

CSO_B clock to out

(330

Ω pull-up resistor required)

10

ns, Min

TSMCO

CCLK to DATA out in readback

9.0

ns, Max

TSMCKBY

CCLK to BUSY out in readback

7.5

ns, Max

FSMCCK

Maximum Frequency with respect to nominal

CCLK.

100

MHz, Max

FRBCCK

Maximum Readback Frequency with respect

to nominal CCLK

60

MHz, Max

FMCCKTOL

Frequency Tolerance with respect to nominal

CCLK.

±50

%

Boundary-Scan Port Timing Specifications

TTAPTCK

TMS and TDI Setup time before TCK

1.0

ns, Min

TTCKTAP

TMS and TDI Hold time after TCK

2.0

ns, Min

TTCKTDO

TCK falling edge to TDO output valid

6

ns, Max

FTCK

Maximum configuration TCK clock frequency

66

MHz, Max

FTCKB

Maximum boundary-scan TCK clock

frequency

66

MHz, Max

相关PDF资料 |

PDF描述 |

|---|---|

| VI-21H-CW-F3 | CONVERTER MOD DC/DC 52V 100W |

| VE-26F-CY-S | CONVERTER MOD DC/DC 72V 50W |

| NCV8505D2T33R4 | IC REG LDO 3.3V .4A D2PAK7 |

| F920J335MPA | CAP TANT 3.3UF 6.3V 20% 0805 |

| R05P209D/R8 | CONV DC/DC 2W 05VIN +/-09VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5VLX110-3FFG676C | 功能描述:IC FPGA VIRTEX-5 110K 676FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LX 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5VLX110T | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-5 Family Overview |

| XC5VLX110T-1FF1136C | 功能描述:IC FPGA VIRTEX-5 110K 1136FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LXT 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5VLX110T-1FF1136CES | 制造商:Xilinx 功能描述: |

| XC5VLX110T-1FF1136I | 功能描述:IC FPGA VIRTEX-5 110K 1136FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LXT 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

发布紧急采购,3分钟左右您将得到回复。