- 您现在的位置:买卖IC网 > PDF目录19298 > XC5VLX110-3FFG1760C (Xilinx Inc)IC FPGA VIRTEX-5 110K 1760FBGA PDF资料下载

参数资料

| 型号: | XC5VLX110-3FFG1760C |

| 厂商: | Xilinx Inc |

| 文件页数: | 82/91页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX-5 110K 1760FBGA |

| 标准包装: | 1 |

| 系列: | Virtex®-5 LX |

| LAB/CLB数: | 8640 |

| 逻辑元件/单元数: | 110592 |

| RAM 位总计: | 4718592 |

| 输入/输出数: | 800 |

| 电源电压: | 0.95 V ~ 1.05 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 1760-BBGA,FCBGA |

| 供应商设备封装: | 1760-FCBGA |

| 配用: | 568-5088-ND - BOARD DEMO DAC1408D750 HW-V5-ML523-UNI-G-ND - EVALUATION PLATFORM VIRTEX-5 HW-AFX-FF1760-500-G-ND - BOARD DEV VIRTEX 5 FF1760 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页当前第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页

Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

DS202 (v5.3) May 5, 2010

Product Specification

83

Source-Synchronous Switching Characteristics

The parameters in this section provide the necessary values for calculating timing budgets for Virtex-5 FPGA

source-synchronous transmitter and receiver data-valid windows.

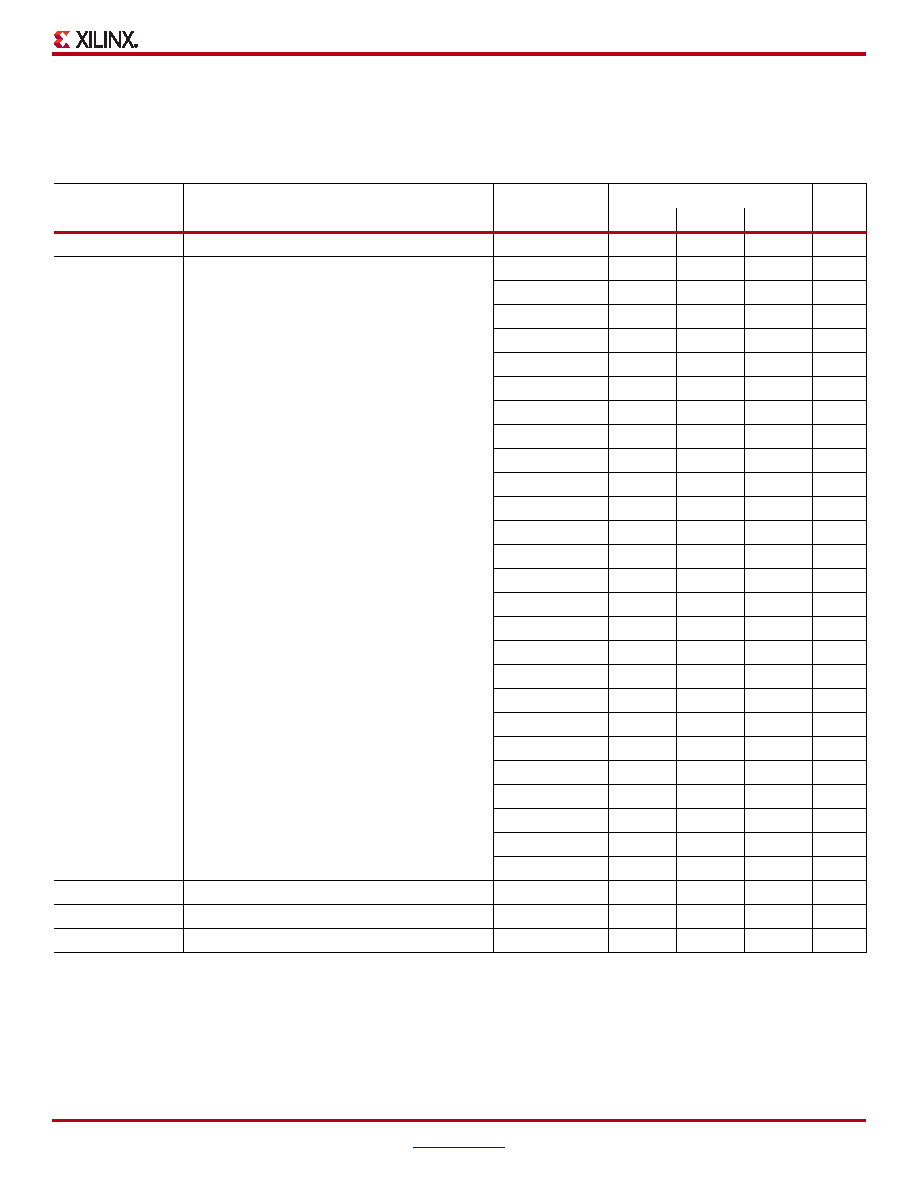

Table 98: Duty Cycle Distortion and Clock-Tree Skew

Symbol

Description

Device

Speed Grade

Units

-3

-2

-1

TDCD_CLK

Global Clock Tree Duty Cycle Distortion(1)

All

0.12

ns

TCKSKEW

Global Clock Tree Skew(2)

XC5VLX20T

N/A

0.24

0.25

ns

XC5VLX30

0.21

0.22

ns

XC5VLX30T

0.21

0.22

ns

XC5VLX50

0.26

0.27

0.28

ns

XC5VLX50T

0.26

0.27

0.28

ns

XC5VLX85

0.42

0.43

0.45

ns

XC5VLX85T

0.42

0.43

0.45

ns

XC5VLX110

0.48

0.50

0.51

ns

XC5VLX110T

0.48

0.50

0.51

ns

XC5VLX155

0.82

0.85

0.88

ns

XC5VLX155T

0.82

0.85

0.88

ns

XC5VLX220

N/A

1.07

1.10

ns

XC5VLX220T

N/A

1.07

1.10

ns

XC5VLX330

N/A

1.25

1.29

ns

XC5VLX330T

N/A

1.25

1.29

ns

XC5VSX35T

0.38

0.39

ns

XC5VSX50T

0.43

0.44

0.45

ns

XC5VSX95T

N/A

0.72

0.74

ns

XC5VSX240T

N/A

1.32

1.36

ns

XC5VTX150T

N/A

0.70

0.73

ns

XC5VTX240T

N/A

0.97

1.00

ns

XC5VFX30T

0.34

0.35

ns

XC5VFX70T

0.41

0.42

0.43

ns

XC5VFX100T

0.82

0.84

0.86

ns

XC5VFX130T

0.82

0.84

0.86

ns

XC5VFX200T

N/A

1.24

1.29

ns

TDCD_BUFIO

I/O clock tree duty cycle distortion

All

0.10

ns

TBUFIOSKEW

I/O clock tree skew across one clock region

All

0.07

0.08

ns

TDCD_BUFR

Regional clock tree duty cycle distortion

All

0.25

ns

Notes:

1.

These parameters represent the worst-case duty cycle distortion observable at the pins of the device using LVDS output buffers. For cases

where other I/O standards are used, IBIS can be used to calculate any additional duty cycle distortion that might be caused by asymmetrical

rise/fall times.

2.

The TCKSKEW value represents the worst-case clock-tree skew observable between sequential I/O elements. Significantly less clock-tree

skew exists for I/O registers that are close to each other and fed by the same or adjacent clock-tree branches. Use the Xilinx FPGA_Editor

and Timing Analyzer tools to evaluate clock skew specific to the application.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-21H-CW-F3 | CONVERTER MOD DC/DC 52V 100W |

| VE-26F-CY-S | CONVERTER MOD DC/DC 72V 50W |

| NCV8505D2T33R4 | IC REG LDO 3.3V .4A D2PAK7 |

| F920J335MPA | CAP TANT 3.3UF 6.3V 20% 0805 |

| R05P209D/R8 | CONV DC/DC 2W 05VIN +/-09VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5VLX110-3FFG676C | 功能描述:IC FPGA VIRTEX-5 110K 676FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LX 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5VLX110T | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-5 Family Overview |

| XC5VLX110T-1FF1136C | 功能描述:IC FPGA VIRTEX-5 110K 1136FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LXT 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5VLX110T-1FF1136CES | 制造商:Xilinx 功能描述: |

| XC5VLX110T-1FF1136I | 功能描述:IC FPGA VIRTEX-5 110K 1136FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LXT 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

发布紧急采购,3分钟左右您将得到回复。