参数资料

| 型号: | XC6SLX150T-2FG484I |

| 厂商: | Xilinx Inc |

| 文件页数: | 7/89页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN 6 484FGGBGA |

| 标准包装: | 60 |

| 系列: | Spartan® 6 LXT |

| LAB/CLB数: | 11519 |

| 逻辑元件/单元数: | 147443 |

| RAM 位总计: | 4939776 |

| 输入/输出数: | 296 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 484-BBGA |

| 供应商设备封装: | 484-FBGA |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

Spartan-6 FPGA Data Sheet: DC and Switching Characteristics

DS162 (v3.0) October 17, 2011

Product Specification

15

GTP Transceiver Switching Characteristics

Consult UG386: Spartan-6 FPGA GTP Transceivers User Guide for further information.

Table 17: GTP Transceiver Clock DC Input Level Specification

Symbol

DC Parameter

Min

Typ

Max

Units

VIDIFF

Differential peak-to-peak input voltage

200

800

2000

mV

RIN

Differential input resistance

80

100

120

CEXT

Required external AC coupling capacitor

–

100

–

nF

Table 18: GTP Transceiver Performance

Symbol

Description

Speed Grade

Units

-3

-3N

-2

-1L

FGTPMAX

Maximum GTP transceiver data rate

3.2

2.7

N/A

Gb/s

FGTPRANGE1

GTP transceiver data rate range when

PLL_TXDIVSEL_OUT = 1

1.88 to 3.2

1.88 to 2.7

N/A

Gb/s

FGTPRANGE2

GTP transceiver data rate range when

PLL_TXDIVSEL_OUT = 2

0.94 to 1.62

N/A

Gb/s

FGTPRANGE3

GTP transceiver data rate range when

PLL_TXDIVSEL_OUT = 4

0.6 to 0.81

N/A

Gb/s

FGPLLMAX

Maximum PLL frequency

1.62

N/A

GHz

FGPLLMIN

Minimum PLL frequency

0.94

N/A

GHz

Table 19: GTP Transceiver Dynamic Reconfiguration Port (DRP) Switching Characteristics

Symbol

Description

Speed Grade

Units

-3

-3N

-2

-1L

FGTPDRPCLK

GTP transceiver DCLK (DRP clock) maximum frequency

125

100

N/A

MHz

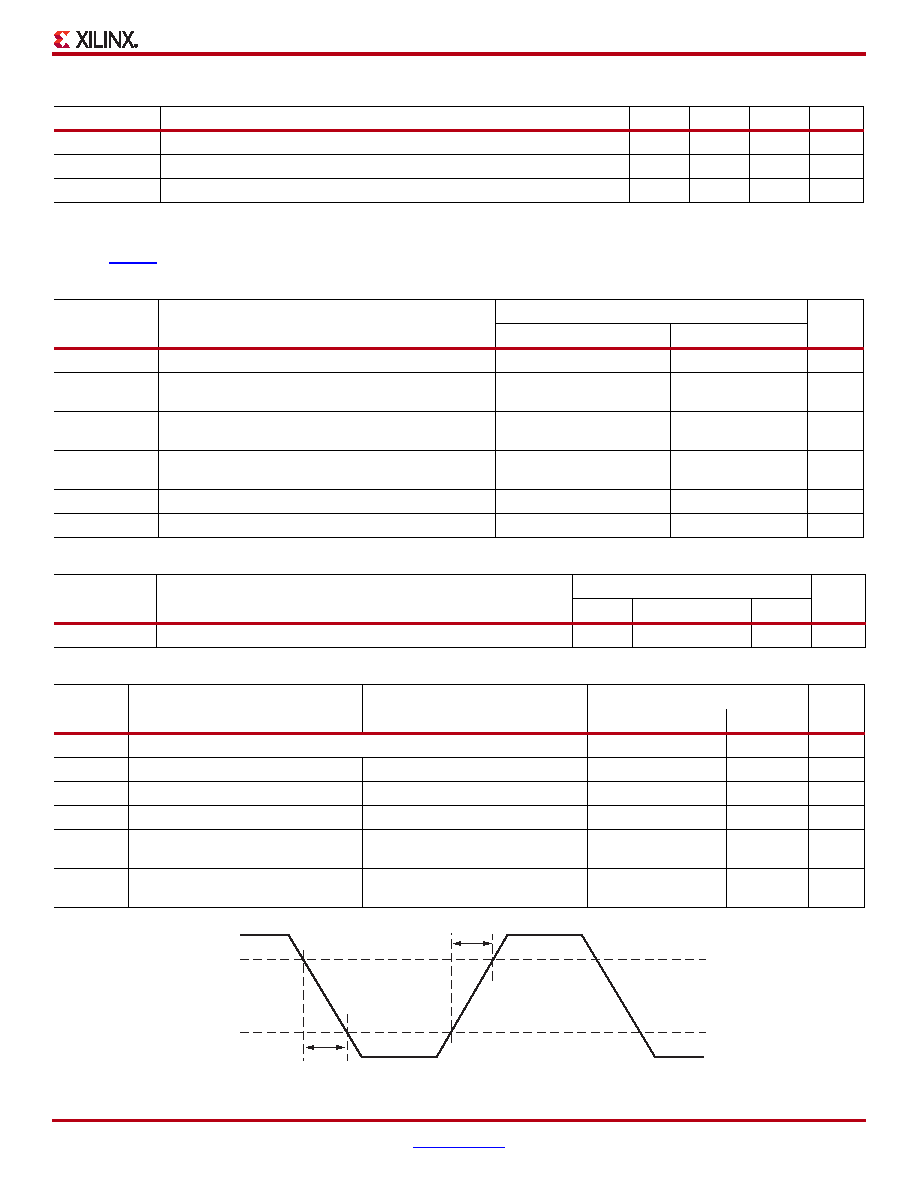

Table 20: GTP Transceiver Reference Clock Switching Characteristics

Symbol

Description

Conditions

All LXT Speed Grades

Units

Min

Typ

Max

FGCLK

Reference clock frequency range

60

–

160

MHz

TRCLK

Reference clock rise time

20% – 80%

–

200

–

ps

TFCLK

Reference clock fall time

80% – 20%

–

200

–

ps

TDCREF

Reference clock duty cycle

Transceiver PLL only

45

50

55

%

TLOCK

Clock recovery frequency acquisition

time

Initial PLL lock

–

1

ms

TPHASE

Clock recovery phase acquisition time Lock to data after PLL has locked to

the reference clock

––

200

s

X-Ref Target - Figure 3

Figure 3: Reference Clock Timing Parameters

ds162_05_042109

80%

20%

TFCLK

TRCLK

相关PDF资料 |

PDF描述 |

|---|---|

| XC6SLX150T-2FGG484I | IC FPGA SPARTAN 6 147K 484FGGBGA |

| 4272-50S | COVER D-SUB 50-F COND (1000PCS) |

| XC6SLX150T-2CSG484I | IC FPGA SPARTAN 6 147K 484CSGBGA |

| 4272-50P | COVER D-SUB 50-M COND (1000PCS) |

| XCV300E-6FG256C | IC FPGA 1.8V C-TEMP 256-FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC6SLX150T-2FG676C | 制造商:Xilinx 功能描述:FPGA SPARTAN?-6 FAMILY 147443 CELLS 45NM (CMOS) TECHNOLOGY 1 - Trays 制造商:Xilinx 功能描述:IC FPGA SPARTAN 6 147K 676BGA 制造商:Xilinx 功能描述:IC FPGA 396 I/O 676FCBGA |

| XC6SLX150T-2FG676I | 功能描述:IC FPGA SPARTAN 6 676FGGBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC6SLX150T-2FG900C | 制造商:Xilinx 功能描述:FPGA SPARTAN?-6 FAMILY 147443 CELLS 45NM (CMOS) TECHNOLOGY 1 - Trays 制造商:Xilinx 功能描述:IC FPGA SPARTAN 6 147K 900BGA |

| XC6SLX150T-2FG900I | 功能描述:IC FPGA SPARTAN 6 900FGGBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC6SLX150T-2FGG484C | 功能描述:IC FPGA SPARTAN 6 147K 484FGGBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan® 6 LXT 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

发布紧急采购,3分钟左右您将得到回复。