- 您现在的位置:买卖IC网 > PDF目录19489 > XCR3064XL-10CS48C (Xilinx Inc)IC ISP CPLD 64 MCELL 3.3V 48-CSP PDF资料下载

参数资料

| 型号: | XCR3064XL-10CS48C |

| 厂商: | Xilinx Inc |

| 文件页数: | 12/12页 |

| 文件大小: | 0K |

| 描述: | IC ISP CPLD 64 MCELL 3.3V 48-CSP |

| 标准包装: | 416 |

| 系列: | CoolRunner XPLA3 |

| 可编程类型: | 系统内可编程(最少 1K 次编程/擦除循环) |

| 最大延迟时间 tpd(1): | 9.1ns |

| 电压电源 - 内部: | 3 V ~ 3.6 V |

| 逻辑元件/逻辑块数目: | 4 |

| 宏单元数: | 64 |

| 门数: | 1500 |

| 输入/输出数: | 40 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-FBGA,CSPBGA |

| 供应商设备封装: | 48-CSBGA(7x7) |

| 包装: | 托盘 |

CoolRunner XPLA3 CPLD

DS012 (v2.5) May 26, 2009

Product Specification

R

JTAG and ISP Interfacing

A number of industry-established methods exist for

JTAG/ISP interfacing with CPLDs and other integrated cir-

cuits. The CoolRunner XPLA3 family supports the following

methods:

Xilinx HW 130

PC Parallel Port

Workstation or PC Serial Port

Embedded Processor

Automated Test Equipment

Third Party Programmers

Xilinx ISP Programming Tools

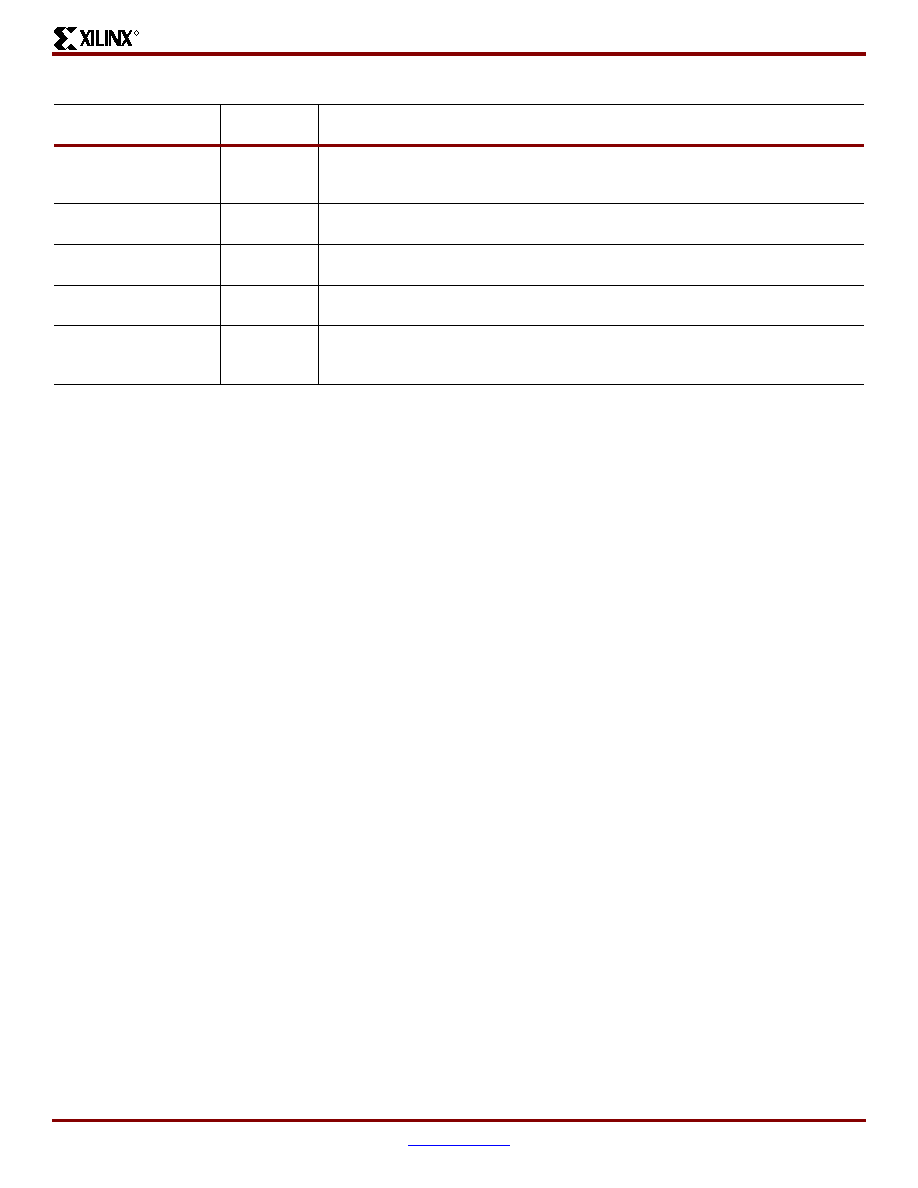

Table 6: Low-level ISP Commands

Instruction

(Register Used)

Instruction

Code

Description

Enable

(ISP Shift Register)

01001

Enables the Erase, Program, and Verify commands. Using the Enable instruction

before the Erase, Program, and Verify instructions allows the user to specify the

outputs of the device using the JTAG Boundary-Scan Sample/Preload command.

Erase

(ISP Shift Register)

01010

Erases the entire EEPROM array. User can define the outputs during this

operation by using the JTAG Sample/Preload command.

Program

(ISP Shift Register)

01011

Programs the data in the ISP Shift Register into the addressed EEPROM row. The

outputs can be defined by using the JTAG Sample/Preload command.

Disable

(ISP Shift Register)

10000

Allows the user to leave ISP mode. It selects the ISP register to be directly

connected between TDO and TDI.

Verify

(ISP Shift Register)

01100

Transfers the data from the addressed row to the ISP Shift Register. The data can

then be shifted out and compared with the JEDEC file. The user can define the

outputs during this operation.

相关PDF资料 |

PDF描述 |

|---|---|

| GCB45DHBR | CONN EDGECARD 90POS R/A .050 SLD |

| DS1722U+ | IC THERMOMETER DIG 3-WIRE 8-USOP |

| ASM24DTBH | CONN EDGECARD 48POS R/A .156 SLD |

| XC9572XL-5VQG44C | IC CPLD 72MCELL 5NS 44-VQFP |

| DS1722S+ | IC DGTL THERMOMETER 3-WIRE 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCR3064XL-10CS48I | 功能描述:IC ISP CPLD 64 MCELL 3.3V 48-CSP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner XPLA3 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XCR3064XL-10CSG48C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 1.5K GATES 64 MCRCLLS 125MHZ 0.35UM 3. - Trays 制造商:Xilinx 功能描述:XLXXCR3064XL-10CSG48C IC SYSTEM GATE |

| XCR3064XL-10CSG48I | 制造商:Xilinx 功能描述:XLXXCR3064XL-10CSG48I IC SYSTEM GATE 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 1.5K GATES 64 MCRCLLS 125MHZ 0.35UM 3. - Trays |

| XCR3064XL-10PC44C | 功能描述:IC ISP CPLD 64 MCELL 3.3V 44PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner XPLA3 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XCR3064XL-10PC44I | 功能描述:IC ISP CPLD 64 MCELL 3.3V 44PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner XPLA3 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。