参数资料

| 型号: | XCS20-3PQ208I |

| 厂商: | Xilinx Inc |

| 文件页数: | 25/83页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 5V I-TEMP 208-PQFP |

| 产品变化通告: | Spartan,Virtex FPGA/SCD Discontinuation 18/Oct/2010 |

| 标准包装: | 24 |

| 系列: | Spartan® |

| LAB/CLB数: | 400 |

| 逻辑元件/单元数: | 950 |

| RAM 位总计: | 12800 |

| 输入/输出数: | 160 |

| 门数: | 20000 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页

Spartan and Spartan-XL FPGA Families Data Sheet

DS060 (v2.0) March 1, 2013

31

Product Specification

R

Product Obsolete/Under Obsolescence

Setting CCLK Frequency

In Master mode, CCLK can be generated in either of two

frequencies. In the default slow mode, the frequency ranges

from 0.5 MHz to 1.25 MHz for Spartan/XL devices. In fast

CCLK mode, the frequency ranges from 4 MHz to 10 MHz

for Spartan/XL devices. The frequency is changed to fast by

an option when running the bitstream generation software.

Data Stream Format

The data stream ("bitstream") format is identical for both

serial configuration modes, but different for the Spartan-XL

family Express mode. In Express mode, the device

becomes active when DONE goes High, therefore no length

count is required. Additionally, CRC error checking is not

supported in Express mode. The data stream format is

shown in Table 16. Bit-serial data is read from left to right.

Express mode data is shown with D0 at the left and D7 at

the right.

The configuration data stream begins with a string of eight

ones, a preamble code, followed by a 24-bit length count

and a separator field of ones (or 24 fill bits, in Spartan-XL

family Express mode). This header is followed by the actual

configuration data in frames. The length and number of

frames depends on the device type (see Table 17).

Each

frame begins with a start field and ends with an error check.

In serial modes, a postamble code is required to signal the

end of data for a single device. In all cases, additional

start-up bytes of data are required to provide four clocks for

the startup sequence at the end of configuration. Long daisy

chains require additional startup bytes to shift the last data

through the chain. All start-up bytes are "don’t cares".

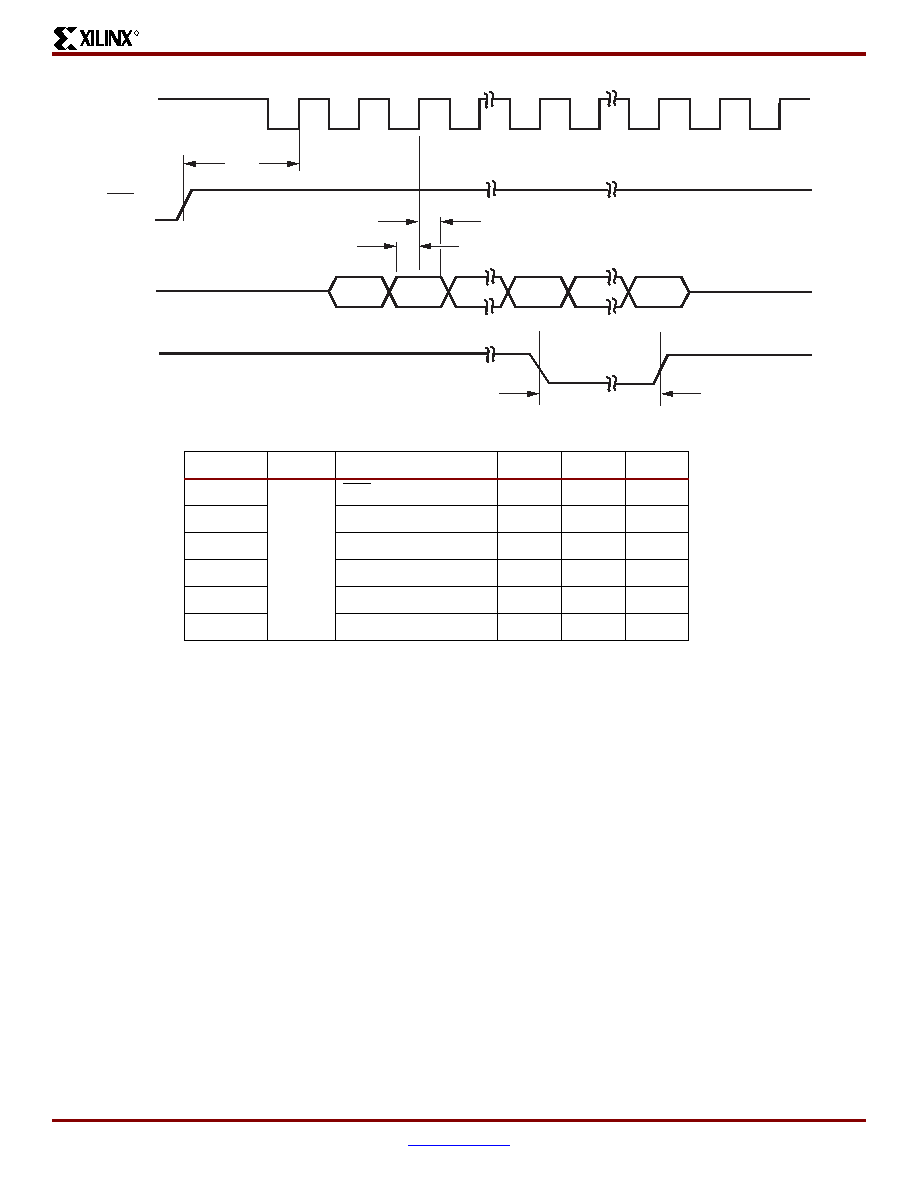

Figure 28: Express Mode Programming Switching Characteristics

DS060_28_080400

BYTE

0

CCLK

FPGA Filled

INIT

TDC

TCD

TIC

D0-D7

DOUT

BYTE

1

BYTE

6

Header Received

Symbol

Description

Min

Max

Units

TIC

CCLK

INIT (High) setup time

5

-

μs

TDC

D0-D7 setup time

20

-

ns

TCD

D0-D7 hold time

0

-

ns

TCCH

CCLK High time

45

-

ns

TCCL

CCLK Low time

45

-

ns

FCC

CCLK Frequency

-

10

MHz

Notes:

1.

If not driven by the preceding DOUT, CS1 must remain High until the

device is fully configured.

相关PDF资料 |

PDF描述 |

|---|---|

| XCS10XL-4VQ100I | IC FPGA 3.3V I-TEMP 100-VQFP |

| KMPC860DEVR80D4 | IC MPU POWERQUICC 80MHZ 357-PBGA |

| FMC65DRAH | CONN EDGECARD 130PS R/A .100 SLD |

| FMC50DREN-S13 | CONN EDGECARD 100POS .100 EXTEND |

| FMC50DREH-S13 | CONN EDGECARD 100POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS20-3PQ240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3PQ240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL FPGA |

| XCS20-3PQ256C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3PQ256I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3PQ280C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。