- 您现在的位置:买卖IC网 > PDF目录225573 > XCV200-6FGG456I (XILINX INC) FPGA, 1176 CLBS, 236666 GATES, 333 MHz, PBGA456 PDF资料下载

参数资料

| 型号: | XCV200-6FGG456I |

| 厂商: | XILINX INC |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1176 CLBS, 236666 GATES, 333 MHz, PBGA456 |

| 封装: | FBGA-456 |

| 文件页数: | 6/24页 |

| 文件大小: | 167K |

| 代理商: | XCV200-6FGG456I |

Virtex 2.5 V Field Programmable Gate Arrays

R

Module 3 of 4

DS003-3 (v3.2) September 10, 2002

14

1-800-255-7778

Production Product Specification

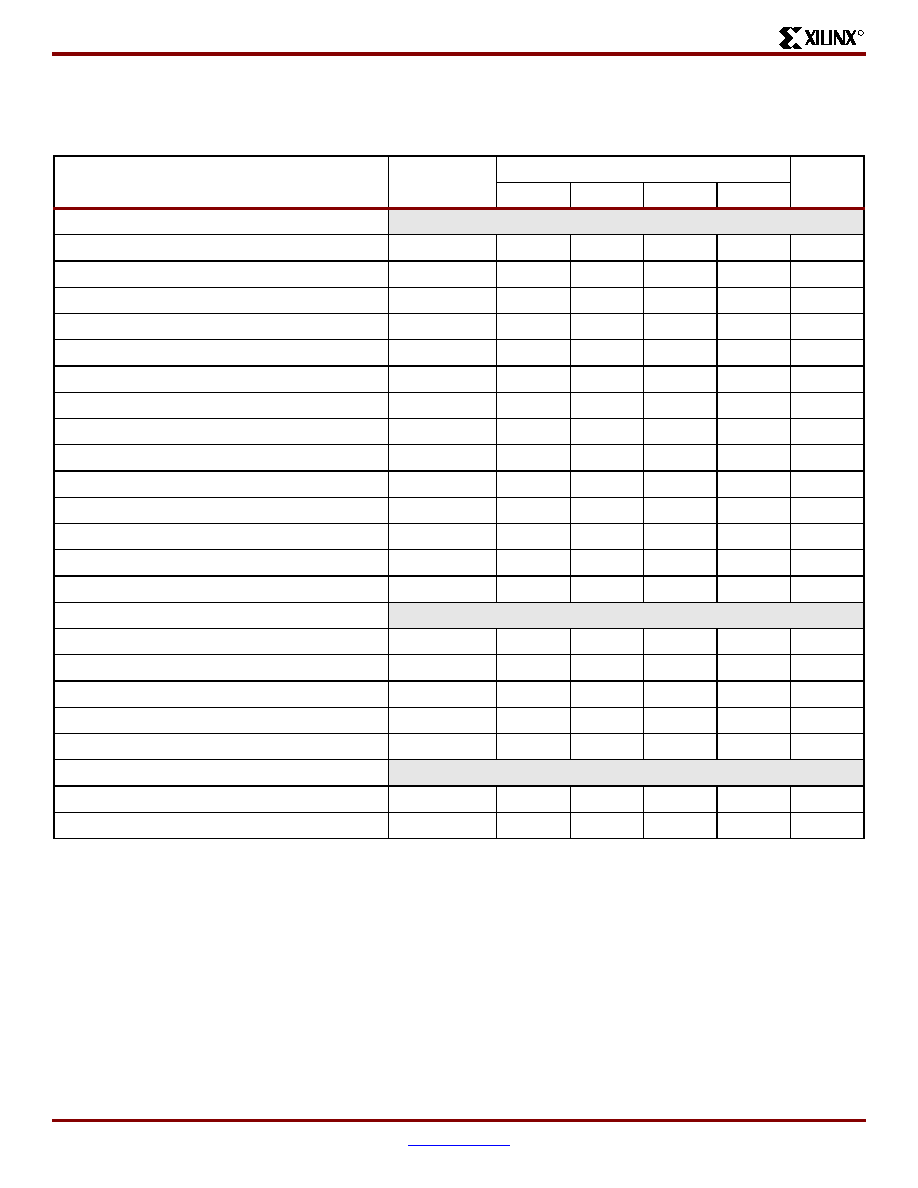

CLB Arithmetic Switching Characteristics

Setup times not listed explicitly can be approximated by decreasing the combinatorial delays by the setup time adjustment

listed. Precise values are provided by the timing analyzer.

Description

Symbol

Speed Grade

Units

Min

-6

-5

-4

Combinatorial Delays

F operand inputs to X via XOR

TOPX

0.37

0.8

0.9

1.0

ns, max

F operand input to XB output

TOPXB

0.54

1.1

1.3

1.4

ns, max

F operand input to Y via XOR

TOPY

0.8

1.5

1.7

2.0

ns, max

F operand input to YB output

TOPYB

0.8

1.5

1.7

2.0

ns, max

F operand input to COUT output

TOPCYF

0.6

1.2

1.3

1.5

ns, max

G operand inputs to Y via XOR

TOPGY

0.46

1.0

1.1

1.2

ns, max

G operand input to YB output

TOPGYB

0.8

1.6

1.8

2.1

ns, max

G operand input to COUT output

TOPCYG

0.7

1.3

1.4

1.6

ns, max

BX initialization input to COUT

TBXCY

0.41

0.9

1.0

1.1

ns, max

CIN input to X output via XOR

TCINX

0.21

0.41

0.46

0.53

ns, max

CIN input to XB

TCINXB

0.02

0.04

0.05

0.06

ns, max

CIN input to Y via XOR

TCINY

0.23

0.46

0.52

0.6

ns, max

CIN input to YB

TCINYB

0.23

0.45

0.51

0.6

ns, max

CIN input to COUT output

TBYP

0.05

0.09

0.10

0.11

ns, max

Multiplier Operation

F1/2 operand inputs to XB output via AND

TFANDXB

0.18

0.36

0.40

0.46

ns, max

F1/2 operand inputs to YB output via AND

TFANDYB

0.40

0.8

0.9

1.1

ns, max

F1/2 operand inputs to COUT output via AND

TFANDCY

0.22

0.43

0.48

0.6

ns, max

G1/2 operand inputs to YB output via AND

TGANDYB

0.25

0.50

0.6

0.7

ns, max

G1/2 operand inputs to COUT output via AND

TGANDCY

0.07

0.13

0.15

0.17

ns, max

Setup and Hold Times before/after Clock CLK(1)

Setup Time / Hold Time

CIN input to FFX

TCCKX/TCKCX

0.50 / 0

1.0 / 0

1.2 / 0

1.3 / 0

ns, min

CIN input to FFY

TCCKY/TCKCY

0.53 / 0

1.1 / 0

1.2 / 0

1.4 / 0

ns, min

Notes:

1.

A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but

if a "0" is listed, there is no positive hold time.

相关PDF资料 |

PDF描述 |

|---|---|

| XCV200-6PQG240I | FPGA, 1176 CLBS, 236666 GATES, 333 MHz, PQFP240 |

| XCV200-6BGG256I | FPGA, 1176 CLBS, 236666 GATES, 333 MHz, PBGA256 |

| XCV200-6BGG352I | FPGA, 1176 CLBS, 236666 GATES, 333 MHz, PBGA352 |

| XD010-04S-D4FY | 350 MHz - 600 MHz RF/MICROWAVE WIDE BAND HIGH POWER AMPLIFIER |

| XF2B-2145-31A | 21 CONTACT(S), FEMALE, STRAIGHT FFC/FPC CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCV200-6PQ240C | 功能描述:IC FPGA 2.5V C-TEMP 240-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex® 标准包装:1 系列:Kintex-7 LAB/CLB数:25475 逻辑元件/单元数:326080 RAM 位总计:16404480 输入/输出数:350 门数:- 电源电压:0.97 V ~ 1.03 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:900-BBGA,FCBGA 供应商设备封装:900-FCBGA(31x31) 其它名称:122-1789 |

| XCV200-6PQ240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XCV200-6PQG240C | 制造商:Xilinx 功能描述:FPGA VIRTEX 236.666K GATES 5292 CELLS 333MHZ 0.22UM 2.5V 240 - Trays |

| XCV200E | 制造商:XILINX 制造商全称:XILINX 功能描述:Field Programmable Gate Arrays |

| XCV200E-6BG240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex⑩-E 1.8 V Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。