参数资料

| 型号: | XR16V554IVTR-F |

| 厂商: | Exar Corporation |

| 文件页数: | 8/43页 |

| 文件大小: | 0K |

| 描述: | IC UART FIFO 16B QUAD 64LQFP |

| 标准包装: | 1,000 |

| 特点: | * |

| 通道数: | 4,QUART |

| FIFO's: | 16 字节 |

| 规程: | RS232 |

| 电源电压: | 2.25 V ~ 3.6 V |

| 带自动流量控制功能: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

XR16V554/554D

16

2.25V TO 3.6V QUAD UART WITH 16-BYTE FIFO

REV. 1.0.3

2.10

Receiver

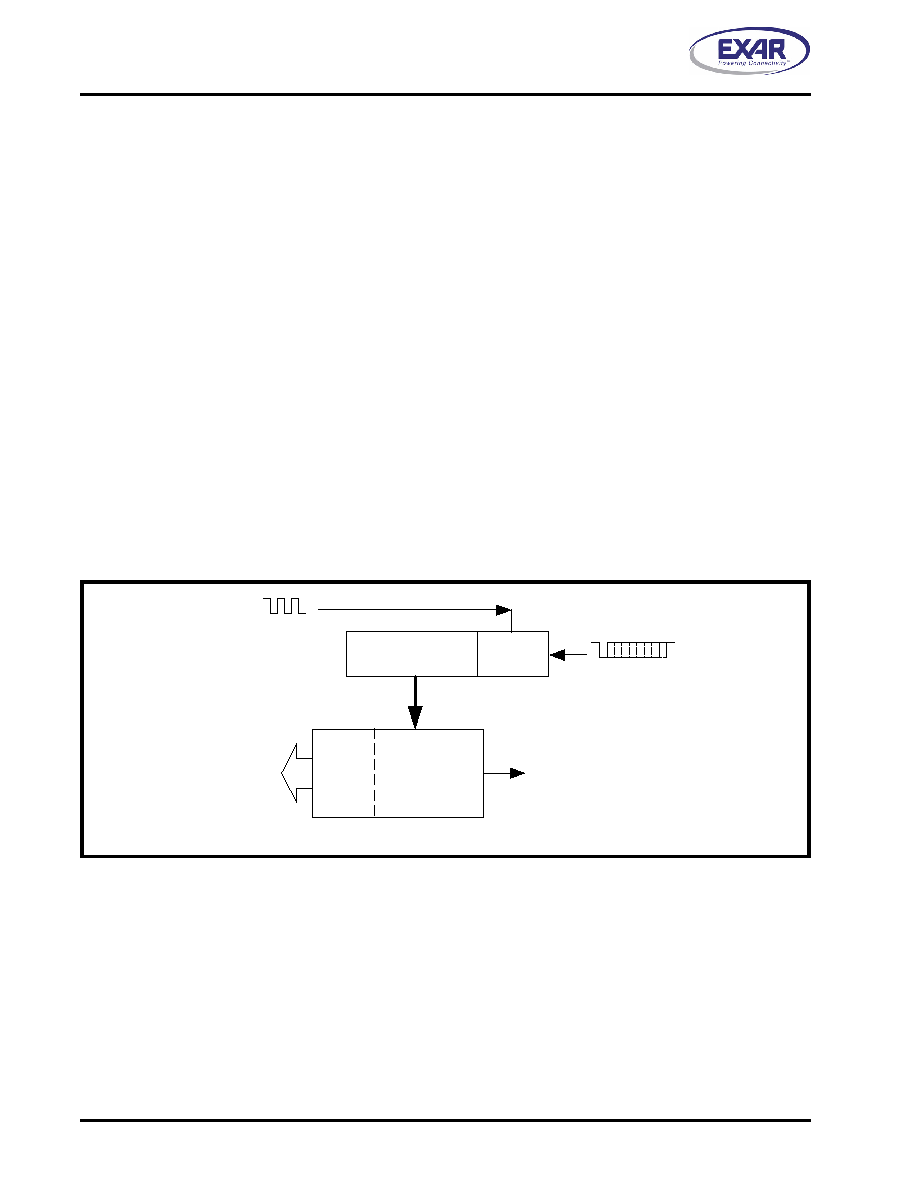

The receiver section contains an 8-bit Receive Shift Register (RSR) and 16 bytes of FIFO which includes a

byte-wide Receive Holding Register (RHR). The RSR uses the 16X clock for timing. It verifies and validates

every bit on the incoming character in the middle of each data bit. On the falling edge of a start or false start bit,

an internal receiver counter starts counting at the 16X clock rate. After 8 clocks the start bit period should be at

the center of the start bit. At this time the start bit is sampled and if it is still LOW it is validated. Evaluating the

start bit in this manner prevents the receiver from assembling a false character. The rest of the data bits and

stop bits are sampled and validated in this same manner to prevent false framing. If there were any error(s),

they are reported in the LSR register bits 2-4. Upon unloading the receive data byte from RHR, the receive

FIFO pointer is bumped and the error tags are immediately updated to reflect the status of the data byte in

RHR register. RHR can generate a receive data ready interrupt upon receiving a character or delay until it

reaches the FIFO trigger level. Furthermore, data delivery to the host is guaranteed by a receive data ready

time-out interrupt when data is not received for 4 word lengths as defined by LCR[1:0] plus 12 bits time. This is

equivalent to 3.7-4.6 character times. The RHR interrupt is enabled by IER bit-0. See Figure 9 and Figure 10

below.

2.10.1

Receive Holding Register (RHR) - Read-Only

The Receive Holding Register is an 8-bit register that holds a receive data byte from the Receive Shift

Register. It provides the receive data interface to the host processor. The RHR register is part of the receive

FIFO of 16 bytes by 11-bit wide, the 3 extra bits are for the 3 error tags to be reported in LSR register. When

the FIFO is enabled by FCR bit-0, the RHR contains the first data character received by the FIFO. After the

RHR is read, the next character byte is loaded into the RHR and the errors associated with the current data

byte are immediately updated in the LSR bits 2-4.

FIGURE 9. RECEIVER OPERATION IN NON-FIFO MODE

Receive Data Shift

Register (RSR)

Receive

Data Byte

and Errors

RHR Interrupt (ISR bit-2)

Receive Data

Holding Register

(RHR)

RXFIFO1

16X Clock

Receive Data Characters

Data Bit

Validation

Error

Tags in

LSR bits

4:2

相关PDF资料 |

PDF描述 |

|---|---|

| XR16V564IJ-F | IC UART FIFO 32B QUAD 68PLCC |

| XR16V598IQ100-F | IC UART FIFO 16B OCTAL 100QFP |

| XR16V654DIV-F | IC UART FIFO 64B QUAD 64LQFP |

| XR16V698IQ100-F | IC UART FIFO 32B OCTAL 100QFP |

| XR16V794IV-F | IC UART FIFO 64B QUAD 64LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16V564 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.25V TO 3.6V QUAD UART WITH 32-BYTE FIFO |

| XR16V564_07 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.25V TO 3.6V QUAD UART WITH 32-BYTE FIFO |

| XR16V564D | 制造商:EXAR 制造商全称:EXAR 功能描述:2.25V TO 3.6V QUAD UART WITH 32-BYTE FIFO |

| XR16V564DIV | 制造商:Rochester Electronics LLC 功能描述: 制造商:Exar Corporation 功能描述: |

| XR16V564DIV-0A-EB | 功能描述:UART 接口集成电路 Supports V564 64 ld LQFP, ISA Interface RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。