- 您现在的位置:买卖IC网 > PDF目录16433 > XR16V598IQ-0A-EVB (Exar Corporation)EVAL BOARD FOR XR16V598-A 100QFP PDF资料下载

参数资料

| 型号: | XR16V598IQ-0A-EVB |

| 厂商: | Exar Corporation |

| 文件页数: | 3/58页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16V598-A 100QFP |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

XR16V598

11

REV. 1.0.3

2.25V TO 3.6V HIGH PERFORMANCE OCTAL UART WITH 16-BYTE FIFO

2.7

Transmitter

The transmitter section comprises of an 8-bit Transmit Shift Register (TSR) and 16 bytes of FIFO which

includes a byte-wide Transmit Holding Register (THR). TSR shifts out every data bit with the 16X or 8X or 4X (if

8X or 4X sampling is selected via the 8XMODE Register or 4XMODE Register) internal clock. A bit time is 16

(or 8 or 4) clock periods. The transmitter sends the start-bit followed by the number of data bits, inserts the

proper parity-bit if enabled, and adds the stop-bit(s). The status of the FIFO and TSR are reported in the Line

Status Register (LSR bit-5 and bit-6).

2.7.1

Transmit Holding Register (THR) - Write Only

The transmit holding register is an 8-bit register providing a data interface to the host processor. The host

writes transmit data byte to the THR to be converted into a serial data stream including start-bit, data bits,

parity-bit and stop-bit(s). The least-significant-bit (Bit-0) becomes first data bit to go out. The THR is the input

register to the transmit FIFO of 16 bytes when FIFO operation is enabled by FCR bit-0. Every time a write

operation is made to the THR, the FIFO data pointer is automatically bumped to the next sequential data

location.

2.7.2

Transmitter Operation in non-FIFO Mode

The host loads transmit data to THR one character at a time. The THR empty flag (LSR bit-5) is set when the

data byte is transferred to TSR. THR flag can generate a transmit empty interrupt (ISR bit-1) when it is enabled

by IER bit-1. The TSR flag (LSR bit-6) is set when TSR becomes completely empty.

400000

3.75

3 12/16

0

3

C

0

460800

3.2552

3 4/16

0

3

4

0.16

500000

3

0

3

0

750000

2

0

2

0

921600

1.6276

1 10/16

0

1

A

0.16

1000000

1.5

1 8/16

0

1

8

0

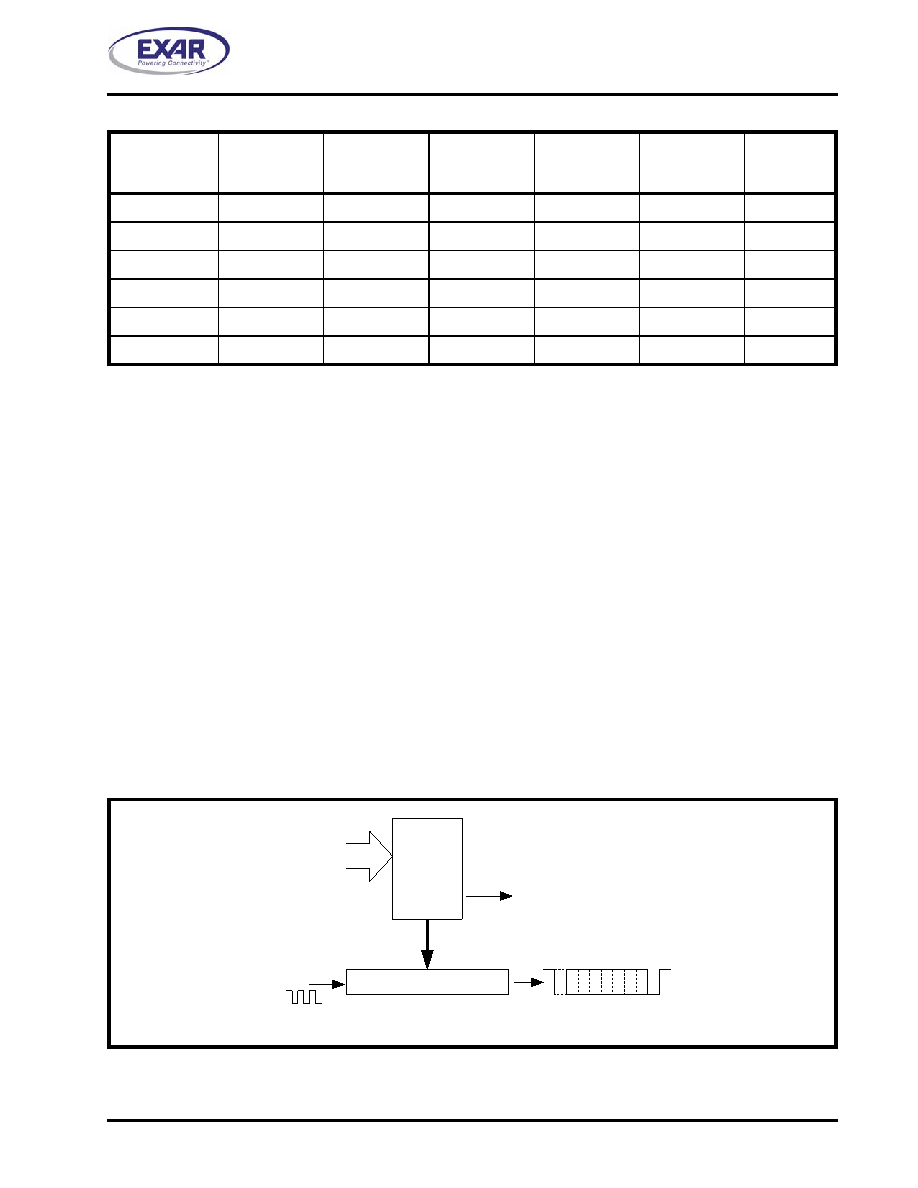

FIGURE 5. TRANSMITTER OPERATION IN NON-FIFO MODE

TABLE 4: TYPICAL DATA RATES WITH A 24 MHZ CRYSTAL OR EXTERNAL CLOCK AT 16X SAMPLING

Required

Output Data

Rate

DIVISOR FOR 16x

Clock

(Decimal)

DIVISOR

OBTAINABLE IN

598

DLM PROGRAM

VALUE (HEX)

DLL PROGRAM

VALUE (HEX)

DLD PROGRAM

VALUE (HEX))

DATA ERROR

RATE (%)

Transmit

Holding

Register

(THR)

Transmit Shift Register (TSR)

Data

Byte

L

S

B

M

S

B

THR Interrupt (ISR bit-1)

Enabled by IER bit-1

TXNOFIFO1

16X or 8X or 4X Clock

相关PDF资料 |

PDF描述 |

|---|---|

| APX809-46SRG-7 | IC MPU RESET CIRC 4.63V SOT23R-3 |

| 176819-000 | SOLDERSLEEVE LO-FIRE 11.5MM DIA |

| XR16M698IQ-0B-EVB | EVAL BOARD FOR M698-B 100QFP |

| XR16M698IQ-0A-EVB | EVAL BOARD FOR M698-A 100QFP |

| A3BBB-3018G | IDC CABLE- ASR30B/AE30G/ASR30B |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16V598IQ-0B-EVB | 功能描述:界面开发工具 Supports V598 100 LD QFP, PCI Interface RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

| XR16V598IQ100 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.25V TO 3.6V HIGH PERFORMANCE OCTAL UART WITH 16-BYTE FIFO |

| XR16V598IQ100-F | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16V654 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.25V TO 3.6V QUAD UART WITH 64-BYTE FIFO |

| XR16V654_0709 | 制造商:EXAR 制造商全称:EXAR 功能描述:2.25V TO 3.6V QUAD UART WITH 64-BYTE FIFO |

发布紧急采购,3分钟左右您将得到回复。