参数资料

| 型号: | XR88C681CP/40-F |

| 厂商: | Exar Corporation |

| 文件页数: | 70/101页 |

| 文件大小: | 0K |

| 描述: | IC UART CMOS DUAL 40PDIP |

| 标准包装: | 9 |

| 特点: | * |

| 通道数: | 2,DUART |

| FIFO's: | 1 字节,3 字节 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 带并行端口: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 通孔 |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 供应商设备封装: | 40-PDIP |

| 包装: | 管件 |

| 其它名称: | 1016-1328-5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页当前第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页

XR88C681

70

Rev. 2.11

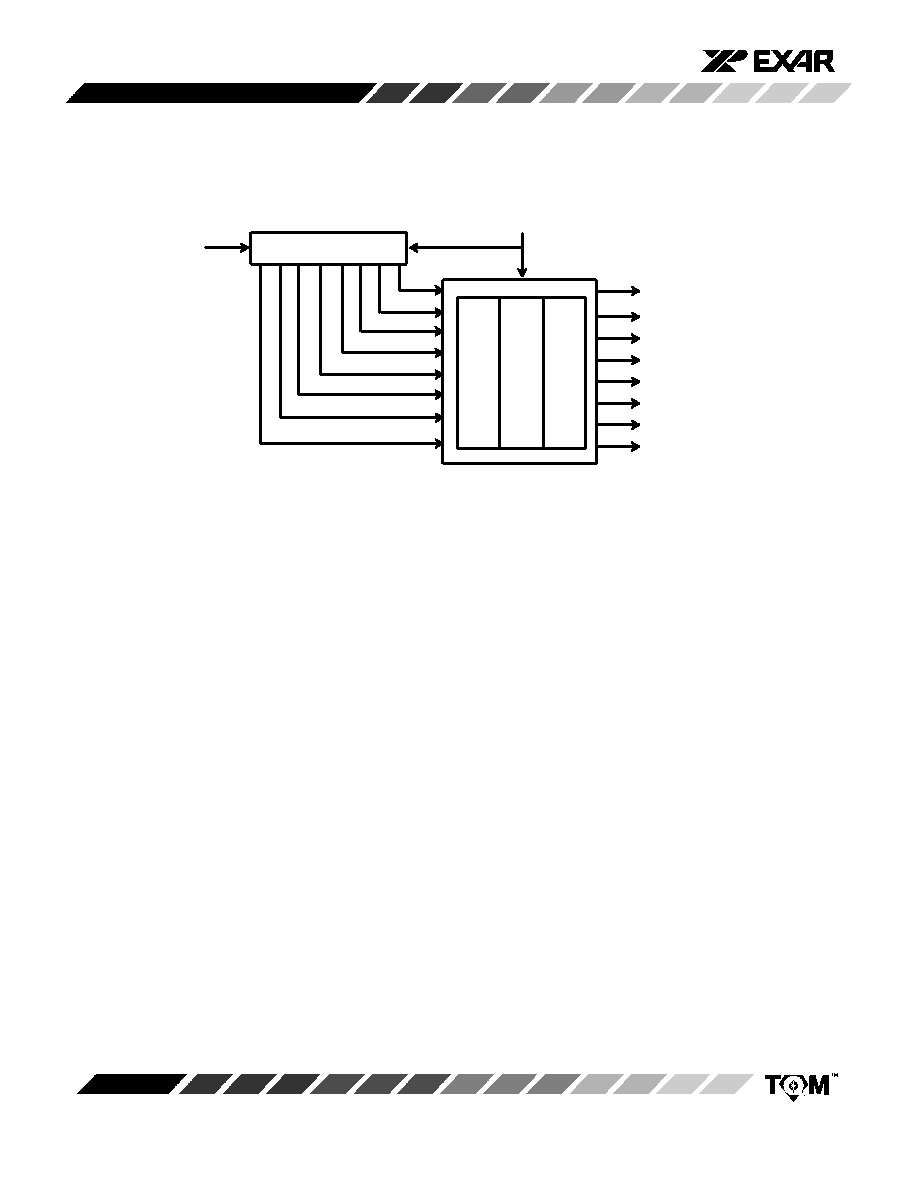

Receive Shift Register

RXDn

Incoming

Serial Data

Receive Holding

Register

RXCn

Receiver Clock (from Timing Block)

To Data Bus

To be read by the CPU

Figure 37. A Simplified Drawing of the Receiver Shift Register

and Receiver Holding Register

The receiver functions by sensing the voltage level at the

RXDn input. When the far-end transmitter is idle, its TXDn

output (and consequently, the RXDn input) is

continuously “marking”. During this period the Receiver is

inactive and is not receiving or processing any data.

However, when the far-end transmitter sends the START

bit, (with its TXDn output toggling “low”), a receiver clock,

which is 16 times the baud rate (with the 16x clock), will

start sampling this START bit. If the receiver determines

that its RXDn input is still “low” after its 7th sample, then

the receiver hardware considers this signal to be a valid

START bit. If the RXDn input is not “low” at the 7th

sample, the Receiver will ignore this downward pulse as

“noise”. From this 7th sample on, the Receiver will

sample each successive bit at one bit-period intervals

(1/baud rate) with the 1x clock. The purpose of this 16x

Clock is then two-fold.

1. To verify that the detected “low” level in the RXDn input

is indeed a START bit.

2. To establish the phase relationship between the 1x bit

sampling clock, and the incoming serial data stream.

The idea is to sample each data bit in the middle of its

bit period.

Please note that if a 16X clock is selected for the receiver,

this over-sampling procedure occurs with each and every

start bit.

The receiver will continue to sample (and receive) each

bit of the character that follows the START bit, at one-bit

time intervals. Upon reception of the character’s MSB the

receiver will check parity (if programmed) or will sample

for the STOP bit. If the Receiver samples a mark

condition at this time and the parity check (if any) was

valid; a successful reception of the character is

presumed; and the Receiver will prepare to sense and

oversample the occurrence of the START bit for the next

character.

相关PDF资料 |

PDF描述 |

|---|---|

| AT89C51RB2-RLRIM | IC MCU FLASH 8051 16K 5V 44-VQFP |

| XR16V2550IM-F | IC UART FIFO 16B 48TQFP |

| MAX7311AWG+T | IC I/O EXPANDER I2C 16B 24SOIC |

| XR16L2750CM-F | IC UART FIFO 64B DUAL 48TQFP |

| XR20M1172IL32-F | IC UART FIFO I2C/SPI 64B 32QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR88C681J | 制造商:Exar Corporation 功能描述: |

| XR88C681J-F | 功能描述:UART 接口集成电路 0.5V-2V UART temp -45 to 85C RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR88C681JTR-F | 功能描述:UART 接口集成电路 Dual Channel UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR88C681MN-S0968 | 制造商:Exar Corporation 功能描述: |

| XR88C681N/40 | 制造商:EXAR 制造商全称:EXAR 功能描述:CMOS DUAL CHANNEL UART (DUART) |

发布紧急采购,3分钟左右您将得到回复。