参数资料

| 型号: | XRT71D04IV |

| 厂商: | Exar Corporation |

| 文件页数: | 19/22页 |

| 文件大小: | 0K |

| 描述: | IC JITTER ATTENUATOR 4CH 80TQFP |

| 标准包装: | 94 |

| 类型: | * |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 4:3 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 44.736MHz |

| 除法器/乘法器: | 无/无 |

| 电源电压: | 3.135 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-LQFP |

| 供应商设备封装: | 80-TQFP(14x14) |

| 包装: | 托盘 |

XRT71D04

á

4 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR, STS-1 TO DS3 DESYNCHRONIZER

REV. 1.1.1

5

23

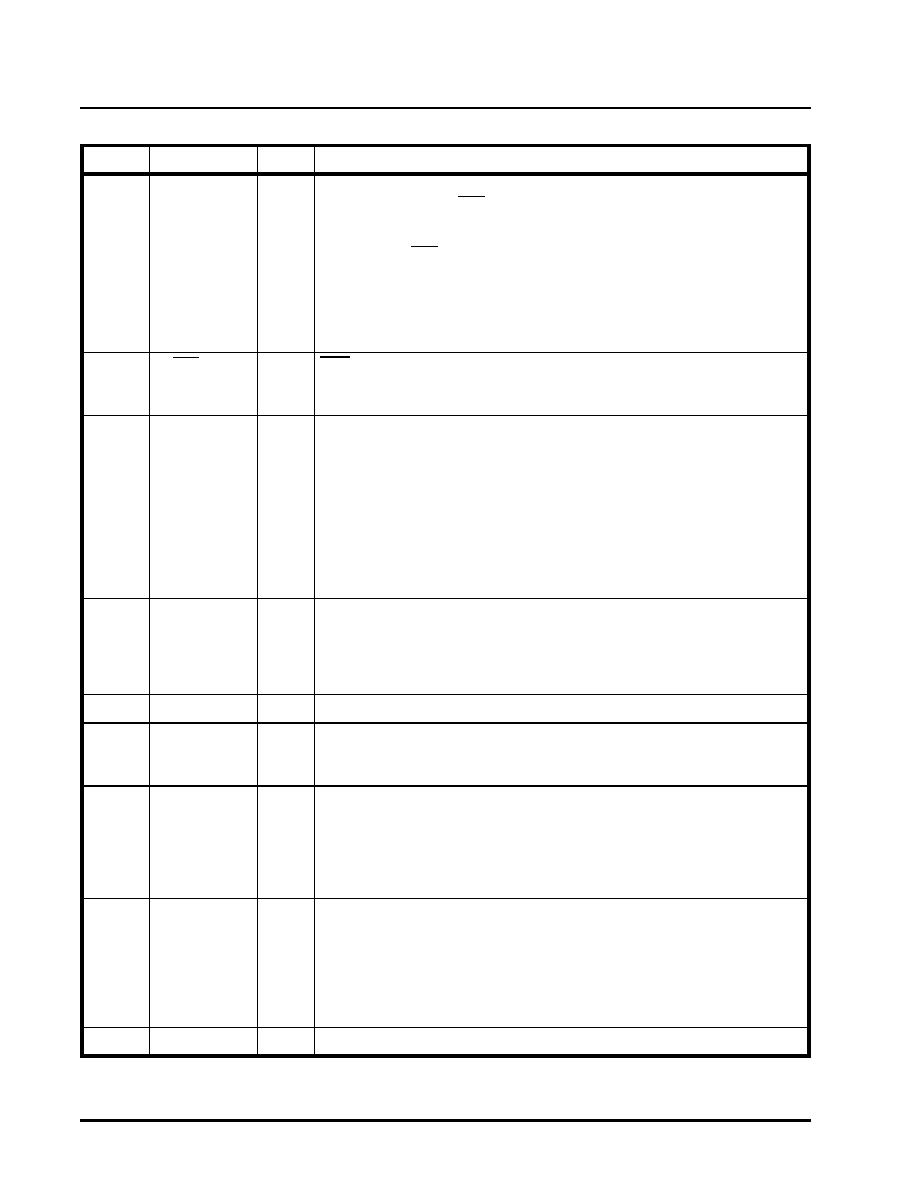

STS1_0

I

SONET STS1 Mode Select - channel 0:

This pin along with the DS3/E3_0 select pin configures the XRT71D04 either in

E3, DS3 or STS-1 mode.

A table relating to the setting of the pins is given below:

STS-1

DS3/E3

XRT71D04 Operating Mode

0

DS3 (44.736 MHz)

0

1

E3 (34.368 MHz)

1

0

STS-1 (51.84 MHz)

1

E3 (34.368 MHz)

This input pin is active only in the Hardware Mode.

24

DS3/E3_0

I

DS3/E3 Select Input - channel 0:

See description pin 10.

Internal 50 K Ohm pull-down resistor.

25

DJA_0/SCLK

I

Harware Mode

Disable Jitter Attenuator Input - Channel 0:

An active-high disables the Jitter Attenuator. The RPOS/RNEG and RCLK will be

passed through without jitter attenuation.

Host Mode

Microprocessor Serial Interface Clock Signal:

This signal will be used to (1) sample the data, on the SDI pin, on the rising edge

of this signal. Additionally, during “Read” operations, the Microprocessor Serial

Interface will update the SDO output on the falling edge of this signal.

Internal 50 K Ohm pull-down resistor.

26

MCLK_3

I

Master Clock Input - channel 3:

Reference clock for internal PLL. 44.736MHz+/-20ppm or 34.368MHz+/-20ppm.

This clock must be continuous and jitter free with duty cycle between 30 to 70%.

It is permissible to use the EXCLK signal orSTS1 clock.

Internal 50 K Ohm pull-up resistor.

27

GND

****

Digital Ground

28

RCLK_3

I

Received Clock (Jittery) - channel 3:

Clock input RCLK3 should be connected to the recovered clock.

Internal 50 K Ohm pull-up resistor.

29

RPOS_2

I

Received Positive Data (Jittery) Input: - channel 2:

Data that is input on this pin is sampled on either the rising or falling edge of

RCLK depending on the setting of the RCLKES pin (pin 10).

If RCLKES is “high”, then RPOS will be sampled on the falling edge of RCLK.

If RCLKES is “low”, then RPOS will be sampled on the rising edge of RCLK.

Internal 50 K Ohm pull-up resistor.

30

RNEG_2

I

Received Negative Data (Jittery) - channel 2:

The input jittery negative data is sampled either on the rising or falling edge of

RCLK depending on the setting of RCLKES.

If RCLKES is “high”, then RNEG will be sampled on the falling edge of RCLK.

If RCLKES is “low”, then RPOS will be sampled on the rising edge of RCLK.

This pin is typically tied to the “RNEG” output pin of the LIU.

Internal 50 K Ohm pull-up resistor.

31

VDD

****

Digital Power Supply = 5V±5% or 3.3V±5%

PIN DESCRIPTION

PIN #NAME

TYPE

DESCRIPTION

相关PDF资料 |

PDF描述 |

|---|---|

| XRT8000IP-F | IC WAN CLOCK E1/E1 DUAL 18PDIP |

| XRT8001IP-F | IC WAN CLOCK E1/E1 DUAL 18PDIP |

| XRT8010IL-F | IC CLK MULTIPLR LVDS 16QFN |

| XRT8020IL-F | IC CLK MULTIPLR LVDS 16QFN |

| XRT91L31IQ | IC TXRX SONET/SDH 8BIT 64QFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT71D04IVTR | 功能描述:时钟合成器/抖动清除器 4CH E3/DS3/STS1 JIT ATTEN DE-SYNCH RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| XRT7250 | 制造商:EXAR 制造商全称:EXAR 功能描述:DS3/E3 FRAMER IC |

| XRT7250ES-PCI | 功能描述:界面开发工具 Evaluation Board for XRT7250 Series RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

| XRT7250IQ100 | 制造商:EXAR 制造商全称:EXAR 功能描述:DS3/E3 FRAMER IC |

| XRT7288 | 制造商:EXAR 制造商全称:EXAR 功能描述:CEPT1 Line Interface |

发布紧急采购,3分钟左右您将得到回复。