参数资料

| 型号: | XRT86VL30IV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 160/175页 |

| 文件大小: | 0K |

| 描述: | IC FRAMR/LIU T1/E1/J1 QD 128LQFP |

| 标准包装: | 72 |

| 控制器类型: | T1/E1/J1 调帧器,LIU |

| 电源电压: | 3.3V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-LQFP |

| 供应商设备封装: | 128-LQFP(14x20) |

| 包装: | 托盘 |

| 其它名称: | 1016-1485 XRT86VL30IV-F-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页当前第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页

XRT86VL30

80

REV. 1.0.1

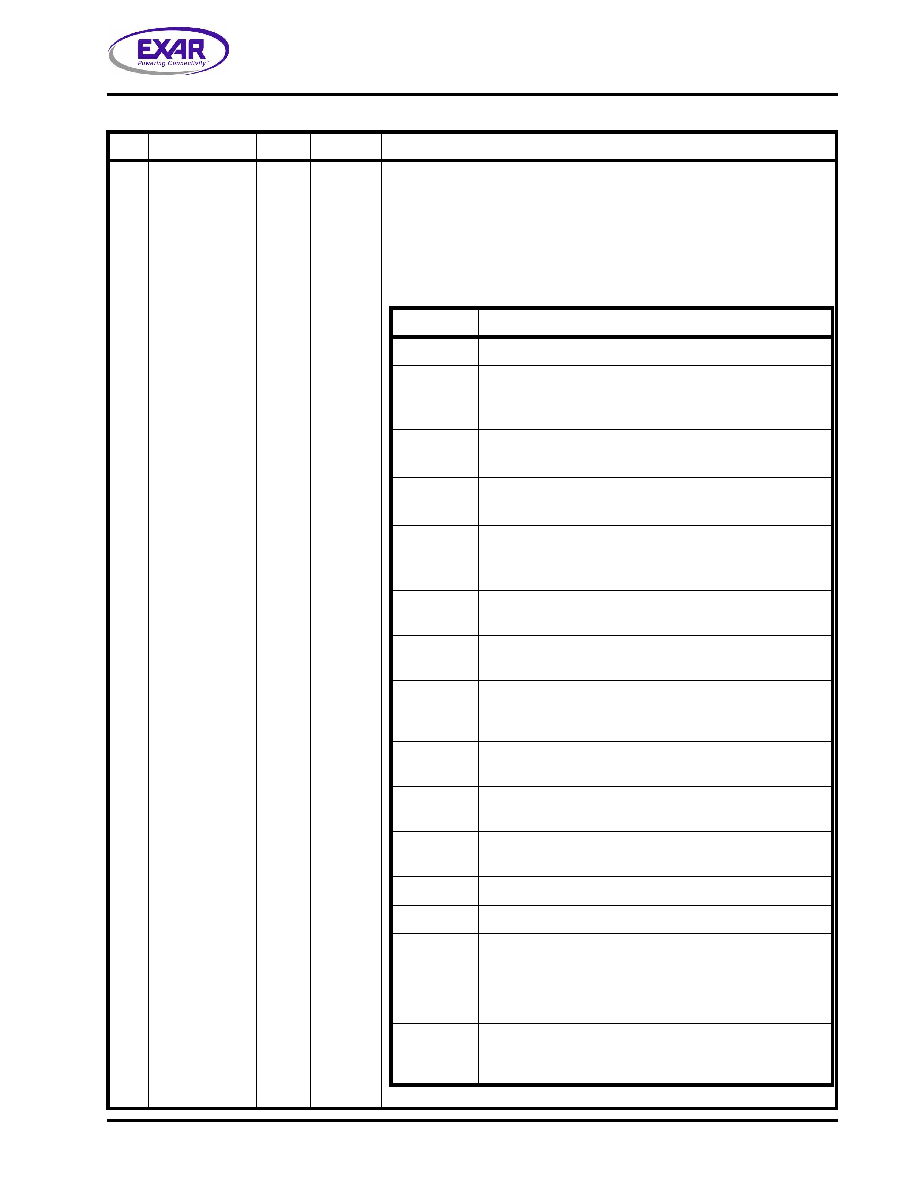

SINGLE T1/E1/J1 FRAMER/LIU COMBO - T1 REGISTER DESCRIPTION

3-0

TxCond(3:0)

R/W

0000

Transmit Channel Conditioning for Timeslot 0 to 23

These bits allow the user to substitute the input PCM data (Octets 0-23)

with internally generated Conditioning Codes prior to transmission to the

remote terminal equipment on a per-channel basis. The table below pre-

sents the different conditioning codes based on the setting of these bits.

Register address 0x0300 represents time slot 0, and address 0x0317 repre-

sents time slot 23.

TABLE 66: TRANSMIT CHANNEL CONTROL REGISTER 0-23 (TCCR 0-23)

HEX ADDRESS: 0X0300 TO 0X0317

BIT

FUNCTION

TYPE

DEFAULT

DESCRIPTION-OPERATION

TXCOND[1:0]

CONDITIONING CODES

0x0 / 0xE

Contents of timeslot octet are unchanged.

0x1

All 8 bits of the selected timeslot octet are inverted (1’s

complement)

OUTPUT = (TIME_SLOT_OCTET) XOR 0xFF

0x2

Even bits of the selected timeslot octet are inverted

OUTPUT = (TIME_SLOT_OCTET) XOR 0xAA

0x3

Odd bits of the selected time slot octet are inverted

OUTPUT = (TIME_SLOT_OCTET) XOR 0x55

0x4

Contents of the selected timeslot octet will be substituted

with the 8 -bit value in the Transmit

Programmable User Code Register (0x0320-0x0337),

0x5

Contents of the timeslot octet will be substituted with the

value 0x7F (BUSY Code)

0x6

Contents of the timeslot octet will be substituted with the

value 0xFF (VACANT Code)

0x7

Contents of the timeslot octet will be substituted with the

BUSY time slot code (111#_####), where ##### is the

Timeslot number

0x8

Contents of the timeslot octet will be substituted with the

MOOF code (0x1A)

0x9

Contents of the timeslot octet will be substituted with the

A-Law Digital Milliwatt pattern

0xA

Contents of the timeslot octet will be substituted with the

-Law Digital Milliwatt pattern

0xB

The MSB (bit 1) of input data is inverted

0xC

All input data except MSB is inverted

0xD

Contents of the timeslot octet will be substituted with the

PRBS X15 + X 14 + 1/QRTS pattern

NOTE: PRBS X15 + X 14 + 1 or QRTS pattern depends on

PRBSType selected in the register 0x0123 - bit 7

0xF

D/E time slot - The TxDE[2:0] bits in the Transmit Signal-

ing and Data Link Select Register (0x010A) will determine

the data source for D/E time slots.

相关PDF资料 |

PDF描述 |

|---|---|

| XRT86VL32IB-F | IC LIU/FRAMER T1/E1/J1 2CH 225BG |

| XRT86VL34IB-F | IC LIU/FRAMER T1/E1/J1 4CH 225BG |

| XRT86VL38IB484-F | IC LIU/FRAMER T1/E1/J1 8CH 484BG |

| XRT86VX38IB329-F | IC TI/E1/J1 FRAMER/LIU 329FPBGA |

| XRT94L31IB-L | IC MAPPER DS3/E3/STS-1 504TBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT86VL30IV-F | 制造商:Exar Corporation 功能描述:T1/E1 Framer Combo IC |

| XRT86VL32 | 制造商:EXAR 制造商全称:EXAR 功能描述:DUAL T1/E1/J1 FRAMER/LIU COMBO - T1 REGISTER DESCRIPTION |

| XRT86VL32_07 | 制造商:EXAR 制造商全称:EXAR 功能描述:DUAL T1/E1/J1 FRAMER/LIU COMBO - E1 REGISTER DESCRIPTION |

| XRT86VL32_0709 | 制造商:EXAR 制造商全称:EXAR 功能描述:DUAL T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION |

| XRT86VL32_1 | 制造商:EXAR 制造商全称:EXAR 功能描述:DUAL T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION |

发布紧急采购,3分钟左右您将得到回复。