- 您现在的位置:买卖IC网 > PDF目录19434 > ZL9101MIRZ (Intersil)MODULE DGTL DC-DC 12A 21QFN PDF资料下载

参数资料

| 型号: | ZL9101MIRZ |

| 厂商: | Intersil |

| 文件页数: | 12/19页 |

| 文件大小: | 0K |

| 描述: | MODULE DGTL DC-DC 12A 21QFN |

| 产品培训模块: | Solutions for Industrial Control Applications |

| 特色产品: | ZL9101M Digital DC/DC Power Module |

| 标准包装: | 96 |

| 系列: | ZL9101M |

| 类型: | 非隔离(POL) |

| 输出数: | 1 |

| 电压 - 输入(最小): | 4.5V |

| 电压 - 输入(最大): | 13.2V |

| Voltage - Output 1: | 0.6 ~ 4 V |

| 电流 - 输出(最大): | 12A |

| 电源(瓦) - 制造商系列: | 48W |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 21-QFN,变式 |

| 尺寸/尺寸: | 0.59" L x 0.59" W x 0.14" H(15.0mm x 15.0mm x 3.5mm) |

| 包装: | 托盘 |

| 工作温度: | -40°C ~ 85°C |

| 效率: | 95% |

| 电源(瓦特)- 最大: | 48W |

�� �

�

�

�ZL9101M�

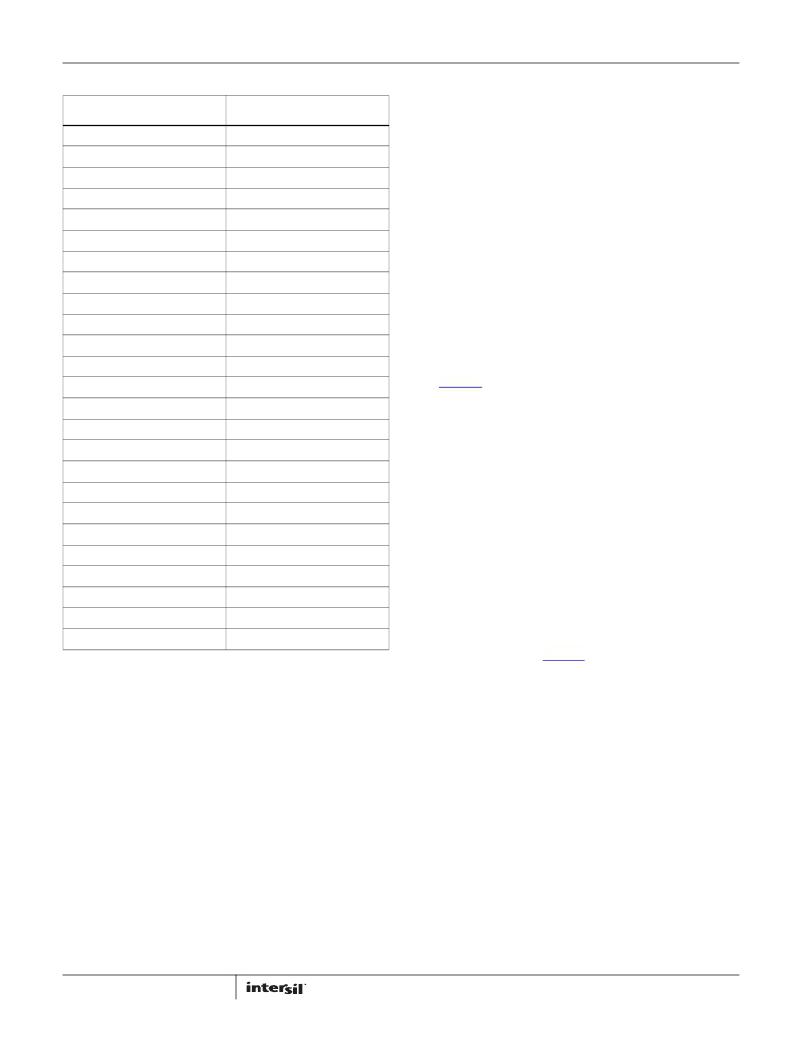

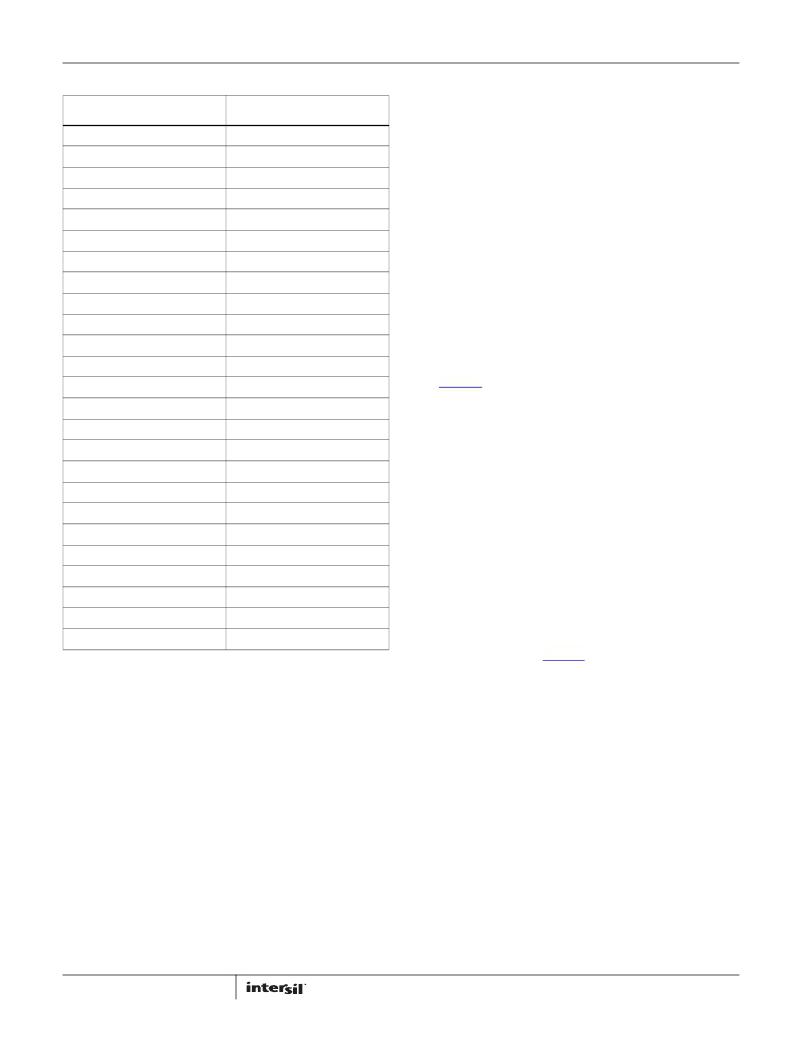

�TABLE� 2.� SMBus� ADDRESS� RESISTOR� SELECTION�

�should� be� limited� to� a� value� that� enables� any� device� to� assert� the�

�bus� to� a� voltage� that� ensures� a� logic� 0� (typically� 0.8V� at� the�

�R� SA� (k� ?� )�

�10�

�11�

�12.1�

�13.3�

�14.7�

�16.2�

�17.8�

�19.6�

�21.5�

�23.7�

�26.1,� or� connect� to� SGND�

�28.7,� or� Open�

�31.6,� or� connect� to� V25� or� VR�

�34.8�

�38.3�

�42.2�

�46.4�

�51.1�

�56.2�

�61.9�

�68.1�

�75�

�82.5�

�90.9�

�100�

�SMBus� ADDRESS�

�0x19�

�0x1A�

�0x1B�

�0x1C�

�0x1D�

�0x1E�

�0x1F�

�0x20�

�0x21�

�0x22�

�0x23�

�0x24�

�0x25�

�0x26�

�0x27�

�0x28�

�0x29�

�0x2A�

�0x2B�

�0x2C�

�0x2D�

�0x2E�

�0x2F�

�0x30�

�0x31�

�device� monitoring� point),� given� the� pull-up� voltage� and� the�

�pull-down� current� capability� of� the� ZL9101M� (nominally� 4mA).�

�Phase� Spreading�

�When� multiple� point-of-load� converters� share� a� common� DC�

�input� supply,� it� is� desirable� to� adjust� the� clock� phase� offset� of�

�each� device� such� that� not� all� devices� start� to� switch�

�simultaneously.� Setting� each� converter� to� start� its� switching� cycle�

�at� a� different� point� in� time,� can� dramatically� reduce� input�

�capacitance� requirements� and� efficiency� losses.� Since� the� peak�

�current� drawn� from� the� input� supply� is� effectively� spread� out� over�

�a� period� of� time,� the� peak� current� drawn� at� any� given� moment� is�

�reduced,� and� the� power� losses� proportional� to� the� I� RMS2� are�

�reduced� dramatically.�

�To� enable� phase� spreading,� all� converters� must� be� synchronized�

�to� the� same� switching� clock.� The� phase� offset� of� each� device�

�may� also� be� set� to� any� value� between� 0°� and� 360°� in� 22.5°�

�increments� via� the� I� 2� C/SMBus� interface.� Refer� to� Application�

�Note� AN2033� for� further� details.�

�Output� Sequencing�

�A� group� of� Digital-DC� modules� or� devices� may� be� configured� to�

�power-up� in� a� predetermined� sequence.� This� feature� is� especially�

�useful� when� powering� advanced� processors,� FPGAs� and� ASICs�

�that� require� one� supply� to� reach� its� operating� voltage;� prior� to�

�another� supply� reaching� its� operating� voltage� in� order� to� avoid�

�latch-up.� Multi-device� sequencing� can� be� achieved� by� configuring�

�each� device� through� the� I� 2� C/SMBus� interface.�

�Multiple� device� sequencing� is� configured� by� issuing� PMBus�

�commands� to� assign� the� preceding� device� in� the� sequencing�

�chain� as� well� as� the� device� that� follows� in� the� sequencing� chain.�

�The� Enable� pins� of� all� devices� in� a� sequencing� group� must� be� tied�

�together� and� driven� high� to� initiate� a� sequenced� turn-on� of� the�

�group.� Enable� must� be� driven� low� to� initiate� a� sequenced� turnoff�

�of� the� group.�

�Digital-DC� Bus�

�The� Digital-DC� Communications� (DDC)� bus� is� used� to�

�communicate� between� Zilker� Labs� Digital-DC� modules� and�

�devices.� This� dedicated� bus� provides� the� communication� channel�

�between� devices� for� features� such� as� sequencing,� fault�

�spreading,� and� current� sharing.� The� DDC� pin� on� all� Digital-DC�

�devices� in� an� application� should� be� connected� together.� A� pull-up�

�resistor� is� required� on� the� DDC� bus� in� order� to� guarantee� the� rise�

�time� as� shown� in� Equation� 1:�

�Refer� to� Application� Note� AN2033� for� details� on� sequencing� via�

�the� I� 2� C/SMBus� interface.�

�Fault� Spreading�

�Digital� DC� modules� and� devices� can� be� configured� to� broadcast� a�

�fault� event� over� the� DDC� bus� to� the� other� devices� in� the� group.�

�When� a� non-destructive� fault� occurs� and� the� device� is� configured�

�to� shut� down� on� a� fault,� the� device� shuts� down� and� broadcasts�

�the� fault� event� over� the� DDC� bus.� The� other� devices� on� the� DDC�

�bus� shut� down� simultaneously,� if� configured� to� do� so,� and�

�Rise� Time� =� R� PU� ?� C� LOAD� ≈� 1� μ� s�

�(EQ.� 1)�

�attempt� to� re-start� in� their� prescribed� order,� if� configured� to�

�do� so.�

�where� R� PU� is� the� DDC� bus� pull-up� resistance� and� C� LOAD� is� the�

�bus� loading.� The� pull-up� resistor� may� be� tied� to� an� external� 3.3V�

�or� 5V� supply� as� long� as� this� voltage� is� present� prior� to� or� during�

�device� power-up.� As� rules� of� thumb,� each� device� connected� to� the�

�DDC� bus� presents� approximately� 10pF� of� capacitive� loading,� and�

�each� inch� of� FR4� PCB� trace� introduces� approximately� 2pF.� The�

�ideal� design� uses� a� central� pull-up� resistor� that� is� well-matched�

�to� the� total� load� capacitance.� The� minimum� pull-up� resistance�

�12�

�Active� Current� Sharing�

�Paralleling� multiple� ZL9101M� modules� can� be� used� to� increase�

�the� output� current� capability� of� a� single� power� rail.� By� connecting�

�the� DDC� pins� of� each� module� together� and� configuring� the�

�modules� as� a� current� sharing� rail,� the� units� share� the� current�

�equally� within� a� few� percent.� Figure� 14� illustrates� a� typical�

�connection� for� two� modules.�

�FN7669.4�

�January� 20,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| EBM18DRKN-S13 | CONN EDGECARD 36POS .156 EXTEND |

| VI-B1F-CY-F1 | CONVERTER MOD DC/DC 72V 50W |

| VI-J32-IZ | CONVERTER MOD DC/DC 15V 25W |

| HWS30-12/A | PWR SUP IND 12V 2.5A SNG OUTPUT |

| 2211-H-RC | INDUCTOR TORD HI AMP 68UH HORZ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL9101MIRZ-T | 功能描述:DCDC DGTL PMBUS MODULE 12A 21QFN RoHS:是 类别:电源 - 板载 >> DC DC Converters 系列:ZL9101M 标准包装:10 系列:PT4570 类型:隔离 输出数:1 电压 - 输入(最小):36V 电压 - 输入(最大):75V Voltage - Output 1:9V Voltage - Output 2:- Voltage - Output 3:- 电流 - 输出(最大):3.3A 电源(瓦) - 制造商系列:30W 电压 - 隔离:1.5kV(1500V) 特点:- 安装类型:表面贴装 封装/外壳:19-SIP SMD 模块 尺寸/尺寸:3.00" L x 1.19" W x 0.50" H(76.2mm x 30.2mm x 12.7mm) 包装:托盘 工作温度:-40°C ~ 85°C 效率:84% 电源(瓦特)- 最大:30W |

| ZL9106MIRZ | 制造商:Intersil Corporation 功能描述:- Bulk |

| ZL9110MIRZ | 制造商:Intersil Corporation 功能描述:- Bulk |

| ZL9117EVAL1Z | 制造商:Intersil Corporation 功能描述:ZL9117EVAL1Z EVALUATION BOARD 1 - 21LD QFN -ROHS COMPLIAN - Bulk 制造商:Intersil Corporation 功能描述:BOARD EVAL FOR ZL9117M 制造商:Intersil Corporation 功能描述:ZL9117EVAL1Z EVALUATION BOARD 1 - 21LD QFN -RoHS COMPLIAN |

| ZL9117M | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Digital DC/DC PMBus 17A Module |

发布紧急采购,3分钟左右您将得到回复。