- 您现在的位置:买卖IC网 > PDF目录206349 > ZPSD403A1V-C-20UI 64K X 16 OTPROM, 40 I/O, PIA-GENERAL PURPOSE, PQFP80 PDF资料下载

参数资料

| 型号: | ZPSD403A1V-C-20UI |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64K X 16 OTPROM, 40 I/O, PIA-GENERAL PURPOSE, PQFP80 |

| 封装: | PLASTIC, TQFP-80 |

| 文件页数: | 95/128页 |

| 文件大小: | 433K |

| 代理商: | ZPSD403A1V-C-20UI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页当前第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页

PSD4XX Family

65

PSD4XX Family

The PSD4XX

Architecture

(cont.)

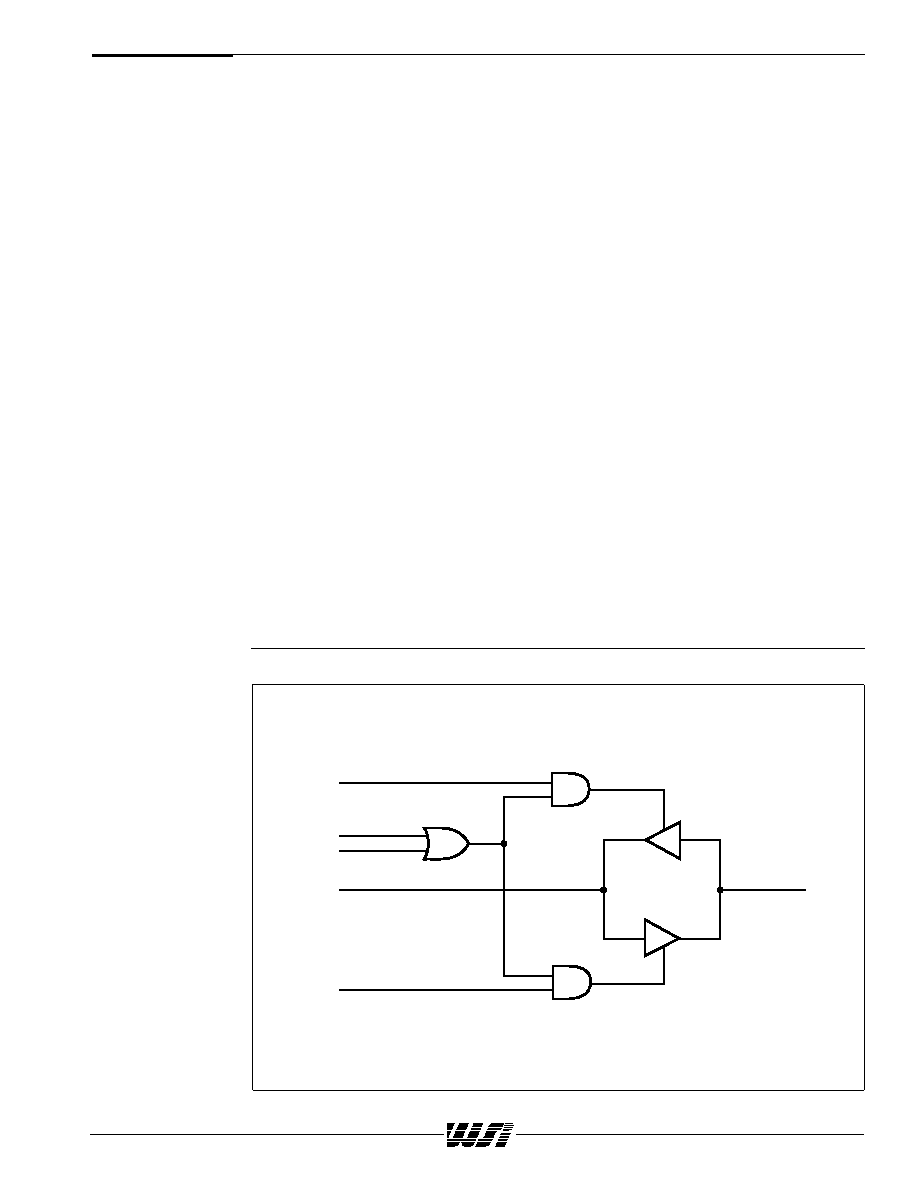

Figure 34. Port A In Peripheral I/O Mode

RD

PSEL0

PSEL1

D0 – D7

WR

PA0 – PA7

9.4.5 Peripheral I/O

The Peripheral I/O Mode is one of the operating modes of Port A. In this mode, Port A

is connected to the data bus of peripheral devices. Port A is enabled only when

the microcontroller is accessing the devices, otherwise the Port is tri-stated. This feature

enables the microcontroller to access external devices without requiring buffers and

decoders. Figure 34 shows the structure of Port A in the Peripheral I/O Mode.

The memory address space occupied by the devices are defined by two signals: PSEL0

and PSEL1. The signals are direct outputs from the Decoding PLD (DPLD). Whenever any

of the signals is active, the Port A driver is enabled, and the direction of the data flow is

determined by the RD/WR signals.

The Peripheral I/O Mode and the peripheral select signals are configured and defined in the

PSDsoft Software (see the section on I/O Port for configuration). The PIO bit in the VM

Register (see Table 17) also needs to be set to “1” by the user to initialize the Peripheral I/O

Mode.

The Peripheral I/O mode can be used, for example, in DMA applications where the

microcontroller does not support DMA operations, such as tri-stating the address/data bus.

Figure 35 shows a block diagram of a microcontroller and PSD4XX based design that

makes use of this mode. In this application, the microcontroller has a multiplexed bus which

is connected to the ADIO port. The C and D ports connect to the peripheral address bus

and are both configured in Address Out Mode. Port A is configured in the Peripheral I/O

mode and is connected to the peripheral data bus. Ports B and E are used to generate

control signals.

During normal activity, the microcontroller has access to any peripheral (memory or I/O

device) through the PSD4XX device. When there is a DMA request, the

microcontroller tri-states the address bus on Ports C and D by writing a “0” to the port

Direction Registers. The DMA controller then takes over the data and address buses after

receiving acknowledgement from the microcontroller.

相关PDF资料 |

PDF描述 |

|---|---|

| ZPSD411A2-C-70U | 32K X 8 OTPROM, 40 I/O, PIA-GENERAL PURPOSE, PQFP80 |

| ZPSD402A2-20JI | 32K X 16 OTPROM, 40 I/O, PIA-GENERAL PURPOSE, PQCC68 |

| ZPSD401A2-70U | 16K X 16 OTPROM, 40 I/O, PIA-GENERAL PURPOSE, PQFP80 |

| ZPSD411A1-90U | 32K X 8 OTPROM, 40 I/O, PIA-GENERAL PURPOSE, PQFP80 |

| ZPSD413A2-15UI | 128K X 8 OTPROM, 40 I/O, PIA-GENERAL PURPOSE, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZPSD403A1V-C-25J | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| ZPSD403A1V-C-25L | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| ZPSD403A1V-C-25U | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Low Cost Field Programmable Microcontroller Peripherals |

| ZPSD403A2-12J | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Peripheral |

| ZPSD403A2-12JI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field-Programmable Peripheral |

发布紧急采购,3分钟左右您将得到回复。