- 您现在的位置:买卖IC网 > PDF目录21904 > 4320-DKDB4 (Silicon Laboratories Inc)KIT DEV TEST EZRADIO SI4320 RX PDF资料下载

参数资料

| 型号: | 4320-DKDB4 |

| 厂商: | Silicon Laboratories Inc |

| 文件页数: | 18/36页 |

| 文件大小: | 0K |

| 描述: | KIT DEV TEST EZRADIO SI4320 RX |

| 标准包装: | 1 |

| 附件类型: | 测试卡,接收器,915MHz |

| 适用于相关产品: | EZRadio? |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

Si4320�

�Bit� 1:� <� ff� >�

�Bit� 0:� <� fe� >�

�Enables� FIFO� fill� after� synchron� word� reception.� FIFO� fill� stops� when� this� bit� is� cleared.�

�Enables� the� 16bit� deep� FIFO� mode.� To� clear� the� FIFO’s� counter� and� content,� it� has� to� be� set� zero.�

�Note:�

�To� restart� the� synchron� word� reception,� bit� 1� should� be� cleared� and� set.� This� action� will� initialize� the� FIFO� and� clear� its� content.�

�Bit� 0� modifies� the� function� of� pin� 6� and� pin� 7.� Pin� 6� (nFFS)� will� become� input� if� fe� is� set� to� 1.� If� the� chip� is� used� in� FIFO� mode,�

�do� not� allow� this� to� be� a� floating� input.�

�11.� Reset� Mode� Command�

�bit�

�15�

�1�

�14�

�1�

�13�

�0�

�12�

�1�

�11�

�1�

�10�

�0�

�9�

�1�

�8�

�0�

�7�

�0�

�6�

�0�

�5�

�0�

�4�

�0�

�3�

�0�

�2�

�0�

�1�

�0�

�0�

�dr�

�POR�

�DA00h�

�Bit� 0� (� dr� ):� Disables� the� highly� sensitive� RESET� mode.� If� this� bit� is� cleared,� a� 600� mV� glitch� in� the� power� supply� may� cause� a� system� reset.� For�

�more� detailed� description� see� the� Reset� modes� section.�

�12.� Status� Read� Command�

�bit�

�15�

�0�

�14�

�0�

�13�

�0�

�12�

�0�

�11�

�0�

�10�

�0�

�9�

�0�

�8�

�0�

�7�

�0�

�6�

�0�

�5�

�0�

�4�

�0�

�3�

�0�

�2�

�0�

�1�

�0�

�0�

�0�

�POR�

�--�

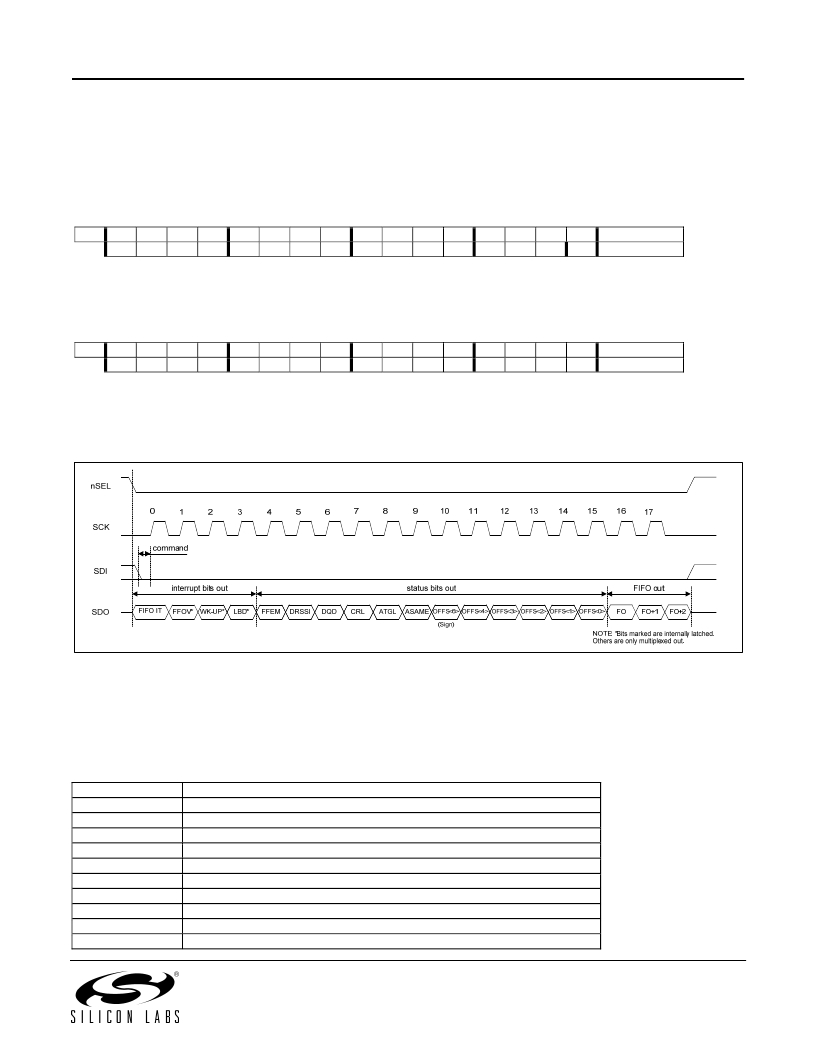

�The� read� command� starts� with� a� zero,� whereas� all� other� control� commands� start� with� a� one.� Therefore,� after� receiving� the� first� bit� of� the�

�control� command� the� Si4320� identifies� it� as� a� read� command.� So� as� the� first� bit� of� the� command� is� received,� the� receiver� starts� to� clock� out�

�the� status� bits� on� the� SDO� output� as� follows:�

�Status� Register� Read� Sequence� with� FIFO� Read� Example�

�It� is� possible� to� read� out� the� content� of� the� FIFO� after� the� reading� of� the� status� bits.� The� command� can� be� aborted� after� any� read� bits� by�

�rising� edge� of� the� select� signal.�

�Note:� The� FIFO� IT� bit� behaves� like� a� status� bit,� but� generates� nIRQ� pulse� if� active.� To� check� whether� there� is� a� sufficient� amount� of� data� in�

�the� FIFO,� the� SDO� output� can� be� tested.� In� extreme� speed� critical� applications,� it� can� be� useful� to� read� only� the� first� four� bits� (� FIFO� IT� -� LBD� )�

�to� clear� the� FFOV,� WK-UP,� and� LBD� bits.� During� the� FIFO� access� the� f� SCK� cannot� be� higher� than� f� ref� /4,� where� f� ref� is� the� crystal� oscillator�

�frequency.� If� the� FIFO� is� read� in� this� mode� the� nFFS� input� must� be� connected� to� logic� high� level.�

�Definitions� of� the� bits� in� the� above� timing� diagram:�

�FIFO� IT�

�FFOV�

�WK-UP�

�LBD�

�FFEM�

�DRSSI�

�DQD�

�CRL�

�ATGL�

�ASAME�

�OFFS6,� 4-0�

�Number� of� the� data� bits� in� the� FIFO� is� reached� the� preprogrammed� limit�

�FIFO� overflow�

�Wake-up� timer� overflow�

�Low� battery� detect,� the� power� supply� voltage� is� below� the� preprogrammed� limit�

�FIFO� is� empty�

�The� strength� of� the� incoming� signal� is� above� the� preprogrammed� limit�

�Data� Quality� Detector� detected� a� good� quality� signal�

�Clock� recovery� lock�

�Toggling� in� each� AFC� cycle�

�AFC� stabilized� (measured� twice� the� same� offset� value)�

�Offset� value� to� be� added� to� the� value� of� the� Frequency� control� word�

�18�

�相关PDF资料 |

PDF描述 |

|---|---|

| PSL0101WBFD1 | LED WHITE 90LM 350MA 3000K SSML |

| PSL0101WBFB1 | LED WHITE 80LM 350MA 3000K SSML |

| V600-IDSC02 | V600 CTRL 2 CH |

| PSL0102WBEC1 | LED WHITE 30LM 120MA 5000K SSML |

| PSL0102WBEB1 | LED WHITE 38LM 120MA 5000K SSML |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 4320-DKDB5 | 功能描述:射频开发工具 Test Board BIFA Rx (868MHz) RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| 4320-DKDB8 | 功能描述:射频开发工具 Test Board xloop Rx (915MHz) RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| 4320-DKDB9 | 功能描述:射频开发工具 Test Board xloop Rx (868Mhz) RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| 4320-L15 | 制造商:American Denki 功能描述: |

| 4320-P | 制造商:American Denki 功能描述: |

发布紧急采购,3分钟左右您将得到回复。