- 您现在的位置:买卖IC网 > PDF目录19555 > 5M1270ZT144A5N (Altera)IC MAX V CPLD 1270 LE 144-TQFP PDF资料下载

参数资料

| 型号: | 5M1270ZT144A5N |

| 厂商: | Altera |

| 文件页数: | 29/30页 |

| 文件大小: | 0K |

| 描述: | IC MAX V CPLD 1270 LE 144-TQFP |

| 产品培训模块: | Max V Overview |

| 特色产品: | MAX? V CPLDs |

| 标准包装: | 60 |

| 系列: | MAX® V |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 6.2ns |

| 电压电源 - 内部: | 1.71 V ~ 1.89 V |

| 逻辑元件/逻辑块数目: | 1270 |

| 宏单元数: | 980 |

| 输入/输出数: | 114 |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-TQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页

�� �

�

�

�Chapter� 3:� DC� and� Switching� Characteristics� for� MAX� V� Devices�

�3–29�

�Timing� Model� and� Specifications�

�JTAG� Timing� Specifications�

��family.�

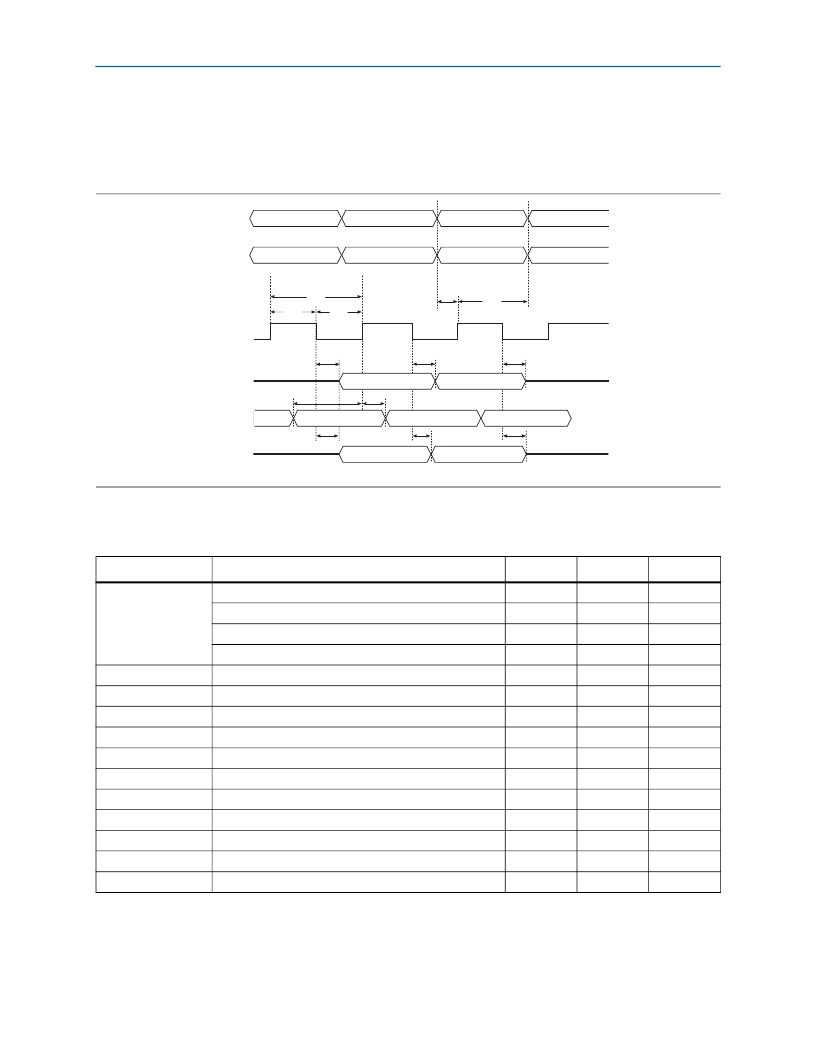

�Figure� 3–6.� JTAG� Timing� Waveform� for� MAX� V� Devices�

�TMS�

�TDI�

�t� JCH�

�t� JCP�

�t� JCL�

�t� JPSU�

�t� JPH�

�TCK�

�TDO�

�t� JPZX�

�t� JPCO�

�t� JPXZ�

�Signal�

�to� be�

�t� JSSU�

�t� JSH�

�Captured�

�t� JSZX�

�t� JSCO�

�t� JSXZ�

�Signal�

�to� be�

�Driven�

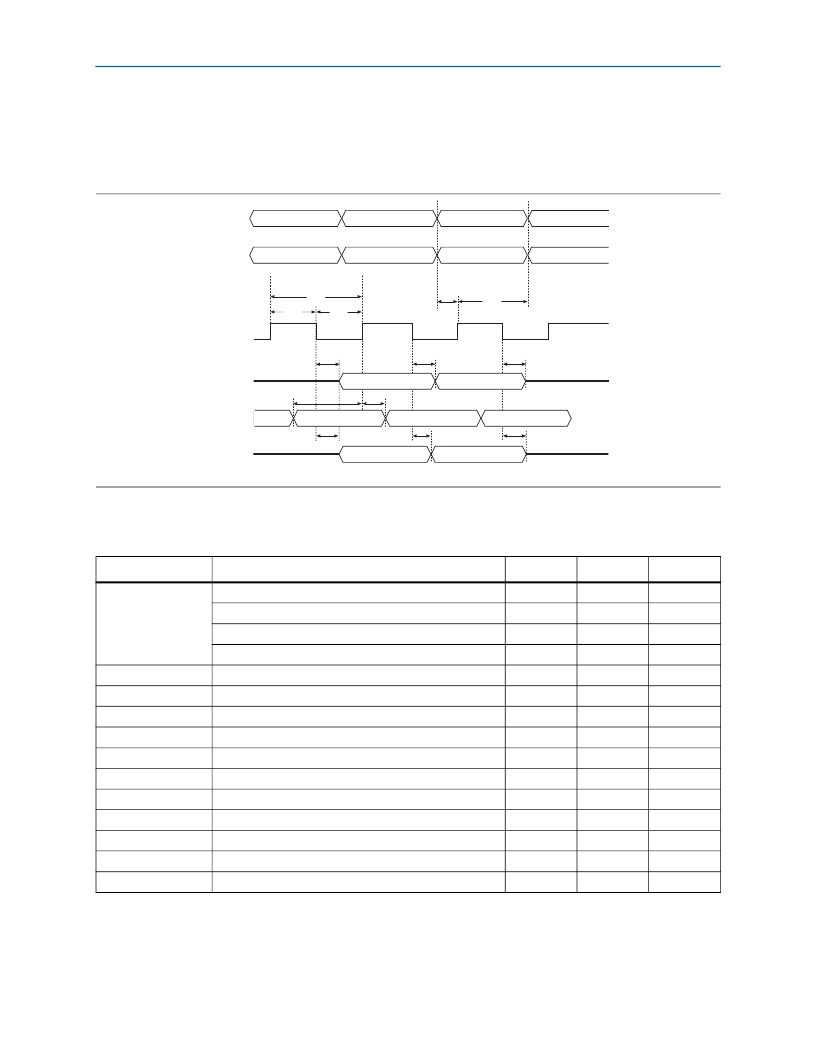

��Table� 3–41.� JTAG� Timing� Parameters� for� MAX� V� Devices� (Part� 1� of� 2)�

�Symbol�

�t� JCP� (1)�

�t� JCH�

�t� JCL�

�t� JPSU�

�t� JPH�

�t� JPCO�

�t� JPZX�

�t� JPXZ�

�t� JSSU�

�t� JSH�

�t� JSCO�

�t� JSZX�

�Parameter�

�TCK� clock� period� for� V� CCIO1� =� 3.3� V�

�TCK� clock� period� for� V� CCIO1� =� 2.5� V�

�TCK� clock� period� for� V� CCIO1� =� 1.8� V�

�TCK� clock� period� for� V� CCIO1� =� 1.5� V�

�TCK� clock� high� time�

�TCK� clock� low� time�

�JTAG� port� setup� time� (2)�

�JTAG� port� hold� time�

�JTAG� port� clock� to� output� (2)�

�JTAG� port� high� impedance� to� valid� output� (2)�

�JTAG� port� valid� output� to� high� impedance� (2)�

�Capture� register� setup� time�

�Capture� register� hold� time�

�Update� register� clock� to� output�

�Update� register� high� impedance� to� valid� output�

�Min�

�55.5�

�62.5�

�100�

�143�

�20�

�20�

�8�

�10�

�—�

�—�

�—�

�8�

�10�

�—�

�—�

�Max�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�15�

�15�

�15�

�—�

�—�

�25�

�25�

�Unit�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�May� 2011�

�Altera� Corporation�

��相关PDF资料 |

PDF描述 |

|---|---|

| ADT7476ARQZ-REEL | IC REMOTE THERMAL CTRR 24QSOP |

| RMM28DSAN | CONN EDGECARD 56POS R/A .156 SLD |

| RSM28DSAH | CONN EDGECARD 56POS R/A .156 SLD |

| EPM570GT100C5 | IC MAX II CPLD 570 LE 100-TQFP |

| GBC06DRXH-S734 | CONN EDGECARD 12POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5M1270ZT144C4N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX V 980 Macro 114 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| 5M1270ZT144C5N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX V 980 Macro 114 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| 5M1270ZT144I5 | 功能描述:IC CPLD 980MC 6.2NS 144TQFP 制造商:altera 系列:MAX? V 包装:托盘 零件状态:有效 可编程类型:系统内可编程 延迟时间 tpd(1)最大值:6.2ns 电源电压 - 内部:1.71 V ~ 1.89 V 逻辑元件/块数:1270 宏单元数:980 栅极数:- I/O 数:114 工作温度:-40°C ~ 100°C(TJ) 安装类型:表面贴装 封装/外壳:144-LQFP 供应商器件封装:144-TQFP(20x20) 标准包装:60 |

| 5M1270ZT144I5N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX V 980 Macro 114 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| 5M1270ZT64A4N | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:MAX V Device Handbook |

发布紧急采购,3分钟左右您将得到回复。