- 您现在的位置:买卖IC网 > PDF目录19543 > 5M2210ZF324I5N (Altera)IC MAX V CPLD 2210 LE 324-FBGA PDF资料下载

参数资料

| 型号: | 5M2210ZF324I5N |

| 厂商: | Altera |

| 文件页数: | 12/30页 |

| 文件大小: | 0K |

| 描述: | IC MAX V CPLD 2210 LE 324-FBGA |

| 产品培训模块: | Max V Overview |

| 特色产品: | MAX? V CPLDs |

| 标准包装: | 84 |

| 系列: | MAX® V |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 7.0ns |

| 电压电源 - 内部: | 1.71 V ~ 1.89 V |

| 逻辑元件/逻辑块数目: | 2210 |

| 宏单元数: | 1700 |

| 输入/输出数: | 271 |

| 工作温度: | -40°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 324-LBGA |

| 供应商设备封装: | 324-FBGA(19x19) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�3–12�

�Chapter� 3:� DC� and� Switching� Characteristics� for� MAX� V� Devices�

�Timing� Model� and� Specifications�

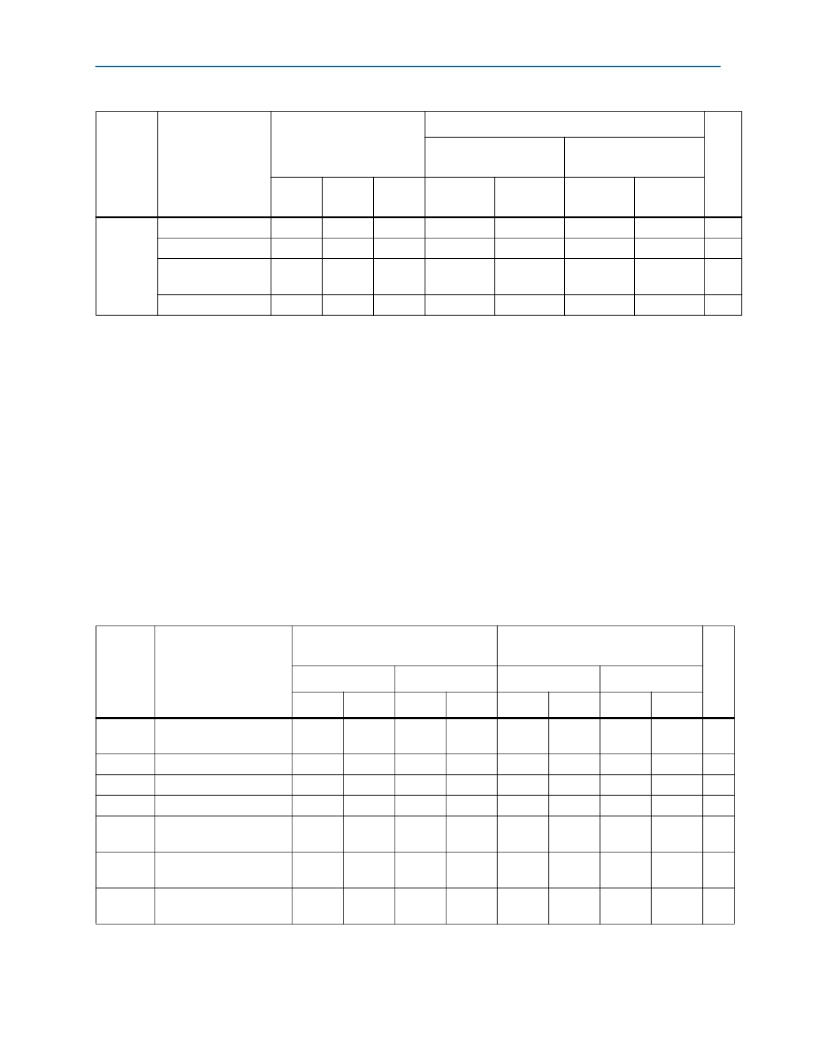

�Table� 3–17.� Device� Performance� for� MAX� V� Devices� (Part� 2� of� 2)�

�Performance�

�Resource�

�Used�

�Design� Size� and�

�Function�

�Resources� Used�

�5M40Z/� 5M80Z/� 5M160Z/�

�5M240Z/� 5M570Z�

�5M1270Z/� 5M2210Z�

�Unit�

�Mode�

�LEs�

�UFM�

�Blocks�

�C4�

�C5,� I5�

�C4�

�C5,� I5�

�512� � 16�

�512� � 16�

�None�

�SPI� (2)�

�3�

�37�

�1�

�1�

�10.0�

�9.7�

�10.0�

�9.7�

�10.0�

�8.0�

�10.0�

�8.0�

�MHz�

�MHz�

�UFM�

�512� � 8�

�512� � 16�

�Parallel�

�(3)�

�I� 2� C� (3)�

�73�

�142�

�1�

�1�

�(4)�

�100� (5)�

�(4)�

�100� (5)�

�(4)�

�100� (5)�

�(4)�

�100� (5)�

�MHz�

�kHz�

��(1)� This� design� is� a� binary� loadable� up� counter.�

�(2)� This� design� is� configured� for� read-only� operation� in� Extended� mode.� Read� and� write� ability� increases� the� number� of� logic� elements� (LEs)� used.�

�(3)� This� design� is� configured� for� read-only� operation.� Read� and� write� ability� increases� the� number� of� LEs� used.�

�(4)� This� design� is� asynchronous.�

�(5)� The� I� 2� C� megafunction� is� verified� in� hardware� up� to� 100-kHz� serial� clock� line� rate.�

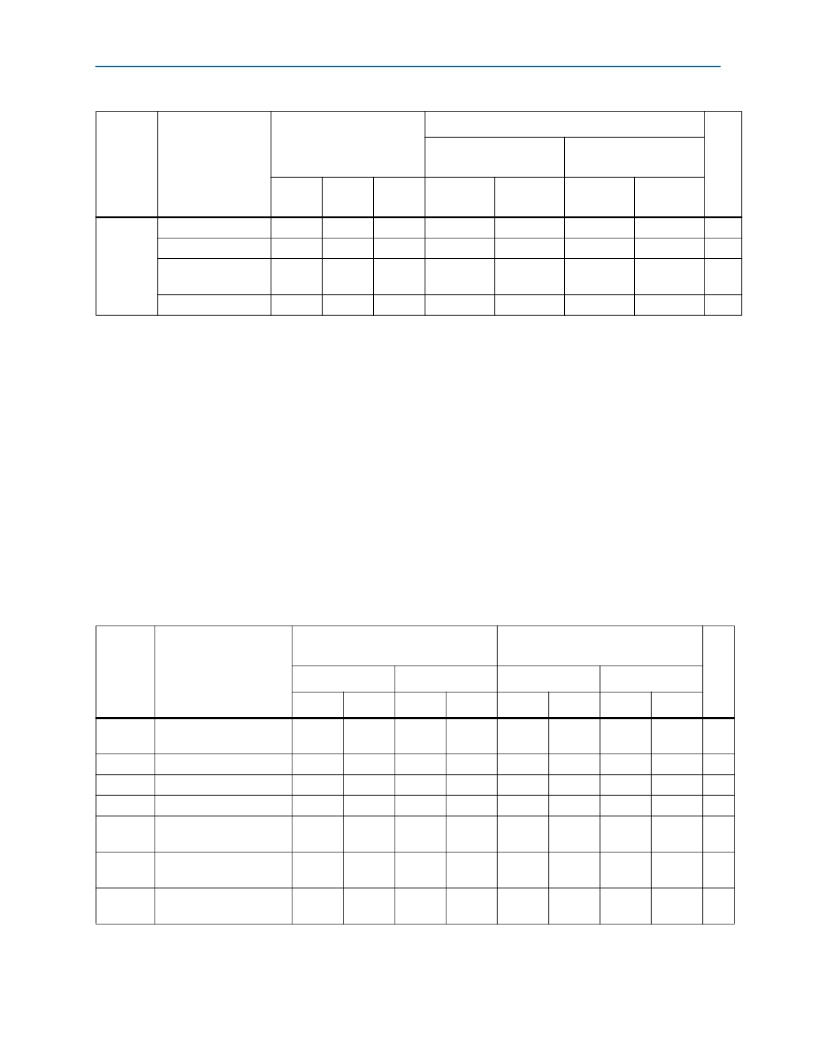

�Internal� Timing� Parameters�

�Internal� timing� parameters� are� specified� on� a� speed� grade� basis� independent� of� device�

�density.� Table� 3–18� through� Table� 3–25� on� page� 3–19� list� the� MAX� V� device� internal�

�timing� microparameters� for� LEs,� input/output� elements� (IOEs),� UFM� blocks,� and�

�MultiTrack� interconnects.�

�f� For� more� information� about� each� internal� timing� microparameters� symbol,� refer� to�

��Table� 3–18.� LE� Internal� Timing� Microparameters� for� MAX� V� Devices� (Part� 1� of� 2)�

�5M40Z/� 5M80Z/� 5M160Z/�

�5M240Z/� 5M570Z�

�5M1270Z/� 5M2210Z�

�Symbol�

�Parameter�

�C4�

�C5,� I5�

�C4�

�C5,� I5�

�Unit�

�Min�

�Max�

�Min�

�Max�

�Min�

�Max�

�Min�

�Max�

�t� LUT�

�t� COMB�

�t� CLR�

�t� PRE�

�t� SU�

�t� H�

�t� CO�

�LE� combinational� look-up�

�table� (LUT)� delay�

�Combinational� path� delay�

�LE� register� clear� delay�

�LE� register� preset� delay�

�LE� register� setup� time�

�before� clock�

�LE� register� hold� time�

�after� clock�

�LE� register�

�clock-to-output� delay�

�—�

�—�

�401�

�401�

�260�

�0�

�—�

�1,215�

�243�

�—�

�—�

�—�

�—�

�380�

�—�

�—�

�545�

�545�

�321�

�0�

�—�

�2,247�

�309�

�—�

�—�

�—�

�—�

�494�

�—�

�—�

�309�

�309�

�271�

�0�

�—�

�742�

�192�

�—�

�—�

�—�

�—�

�305�

�—�

�—�

�381�

�381�

�333�

�0�

�—�

�914�

�236�

�—�

�—�

�—�

�—�

�376�

�ps�

�ps�

�ps�

�ps�

�ps�

�ps�

�ps�

��May� 2011�

�Altera� Corporation�

�相关PDF资料 |

PDF描述 |

|---|---|

| EBA18DRMS | CONN EDGECARD 36POS .125 SQ WW |

| ACC31DRYI | CONN EDGECARD 62POS .100 DIP SLD |

| 5M2210ZF324C4N | IC MAX V CPLD 2210 LE 324-FBGA |

| VE-B0W-CX-B1 | CONVERTER MOD DC/DC 5.5V 75W |

| EPM1270M256C5N | IC MAX II CPLD 1270 LE 256-MBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5M2210ZF64A4N | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:MAX V Device Handbook |

| 5M2210ZF64C5N | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:MAX V Device Handbook |

| 5M2210ZF64I4N | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:MAX V Device Handbook |

| 5M2210ZM64A4N | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:MAX V Device Handbook |

| 5M2210ZM64A5N | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:MAX V Device Handbook |

发布紧急采购,3分钟左右您将得到回复。