- 您现在的位置:买卖IC网 > PDF目录2058 > 5P49EE801NDGI (IDT, Integrated Device Technology Inc)IC CLOCK GENERATOR 28QFN PDF资料下载

参数资料

| 型号: | 5P49EE801NDGI |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 27/27页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GENERATOR 28QFN |

| 标准包装: | 75 |

| 系列: | VersaClock™ |

| 类型: | 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVTTL,晶体 |

| 输出: | LVCMOS,LVDS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:7 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 150MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-VFQFN 裸露焊盘 |

| 供应商设备封装: | 28-VFQFPN(4x4) |

| 包装: | 管件 |

| 其它名称: | 800-2524 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页

IDT5P49EE801

VERSACLOCK LOW POWER CLOCK GENERATOR

EEPROM CLOCK GENERATOR

IDT VERSACLOCK LOW POWER CLOCK GENERATOR

9

IDT5P49EE801

REV M 072512

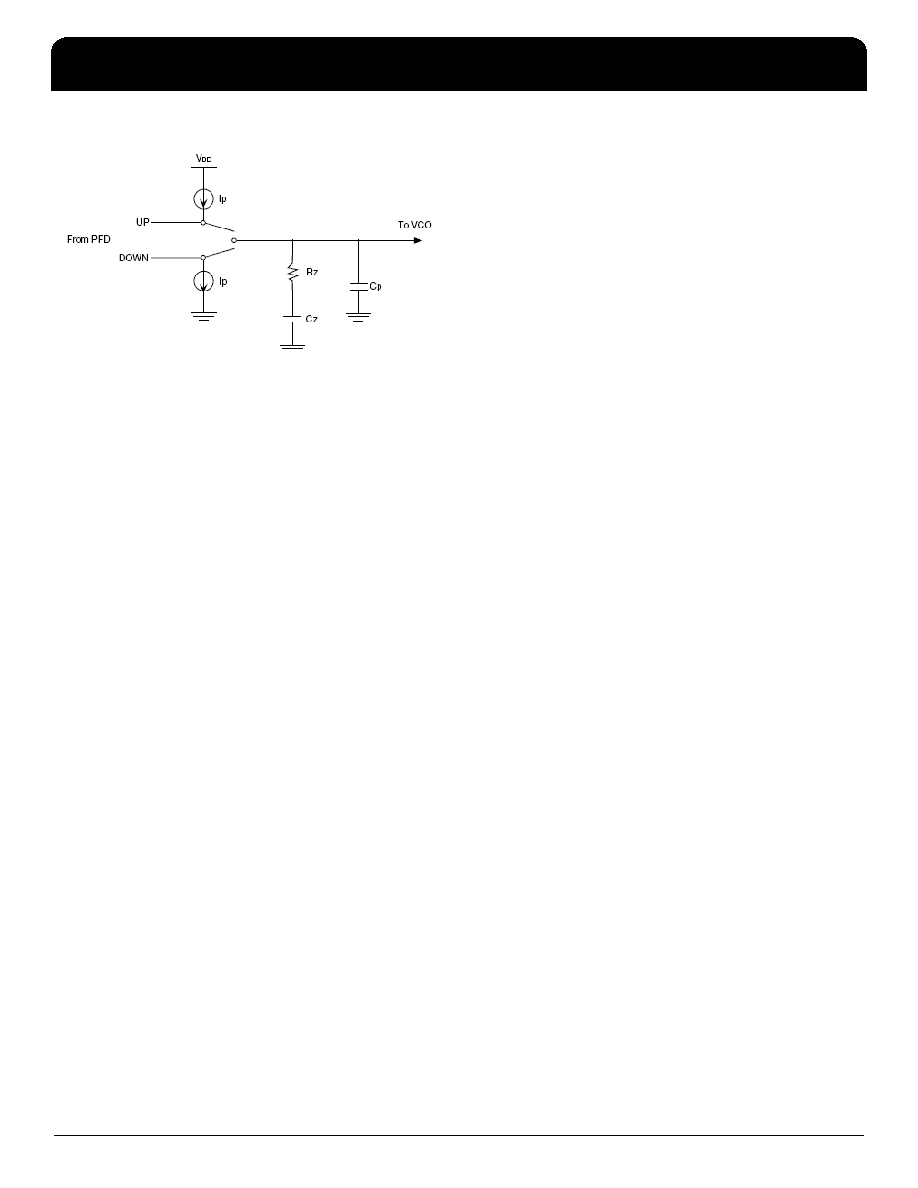

PLL Loop Bandwidth:

Charge pump gain (K

φ) = Ip / 2π

VCO gain (KVCO) = 350MHz/V * 2

π

M = Total multiplier value (See the PRE-SCALERS,

FEEDBACK-DIVIDERS, POST-DIVIDERS section for more

detail)

ωc = (Rz * Kφ * KVCO * Cz)/(M * (Cz + Cp))

Fc =

ωc / 2π

Note, the phase/frequency detector frequency (FPFD) is

typically seven times the PLL closed-loop bandwidth (Fc)

but too high of a ratio will reduce your phase margin thus

compromising loop stability.

To determine if the loop is stable, the phase margin (

φm)

would need to be calculated as follows.

Phase Margin:

ωz = 1 / (Rz * Cz)

ωp = (Cz + Cp)/(Rz * Cz * Cp)

φm = (360 / 2π) * [tan-1(ωc/ ωz) - tan-1(ωc/ ωp)]

To ensure stability in the loop, the phase margin is

recommended to be > 60° but too high will result in the lock

time being excessively long. Certain loop filter parameters

would need to be compromised to not only meet a required

loop bandwidth but to also maintain loop stability.

Damping Factor:

ζ= Rz/2 *(KVCO * Ip * Cz)1/2/M

Example

Fc = 150KHz is the desired loop bandwidth. The total A*M

value is 160. The

ζ(damping factor) target should be 0.7,

meaning the loop is critically damped. Given Fc and A*M, an

optimal loop filter setting needs to be solved for that will

meet both the PLL loop bandwidth and maintain loop

stability.

Choose a mid-range charge pump from register table

Icp= 11.9uA.

K

φ * KVCO = 350MHz/V * 40uA = 12000A/Vs

ωc = 2π * Fc = 9.42x105 s-1

ωp = (Cz + Cp)/(Rz * Cz * Cp) = ωz (1 + Cz / Cp)

Solving for Rz, the best possible value Rz=30kOhms

(RZ[1:0]=10) gives

ζ= 1.4 (Ideal range for ζ is 0.7 to 1.4)

Solving back for the PLL loop bandwidth, Fc=149kHz.

The phase margin must be checked for loop stability.

φm = (360 / 2π) * [tan-1 (9.42x105 s-1 / 1.19x105s-1)

- tan-1(9.42x105 s-1/ 1.23x106 s-1)] = 45°

The phase margin would be acceptable with a fairly stable

loop.

相关PDF资料 |

PDF描述 |

|---|---|

| 74ABT16240ADGG,518 | IC INVERTER QUAD 4-INPUT 48TSSOP |

| 74ABT16244ADGG,518 | IC BUFF DVR TRI-ST 16BIT 48TSSOP |

| 74ABT2240PW,118 | IC INVERTER DUAL 4-INPUT 20TSSOP |

| 74ABT620PW,118 | IC TRANSCVR 3ST 8BIT INV 20TSSOP |

| 74ABT827DB,112 | IC BUFF DVR TRI-ST 10BIT 24SSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5P49EE801NDGI8 | 功能描述:时钟发生器及支持产品 VERSACLOCK LOW POWER PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 5P49EE802-007NDGI | 制造商:Integrated Device Technology Inc 功能描述: |

| 5P49EE802NDGI | 功能描述:时钟发生器及支持产品 VERSACLOCK LOW POWER PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| 5P49EE802NDGI8 | 制造商:Integrated Device Technology Inc 功能描述:Programmable PLL Clock Generator Quad 28-Pin VFQFPN T/R 制造商:Integrated Device Technology Inc 功能描述:28 QFN (4X4MM) - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:VERSACLOCK LOW POWER PLL |

| 5P49EE805NDGI | 制造商:Integrated Device Technology Inc 功能描述:Programmable PLL Clock Generator Quad 28-Pin VFQFPN Tube 制造商:Integrated Device Technology Inc 功能描述:28 QFN (GREEN) - Bulk 制造商:Integrated Device Technology Inc 功能描述:PROGRAMMABLE PLL LOW POWER |

发布紧急采购,3分钟左右您将得到回复。