- 您现在的位置:买卖IC网 > PDF目录20601 > 71M6532F-IGT/F (Maxim Integrated)IC ENERGY METER 256KB 100-LQFP PDF资料下载

参数资料

| 型号: | 71M6532F-IGT/F |

| 厂商: | Maxim Integrated |

| 文件页数: | 25/121页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METER 256KB 100-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 90 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页

�� �

�

�

�FDS� 6531/6532� 005�

�Data� Sheet� 71M6531D/F-71M6532D/F�

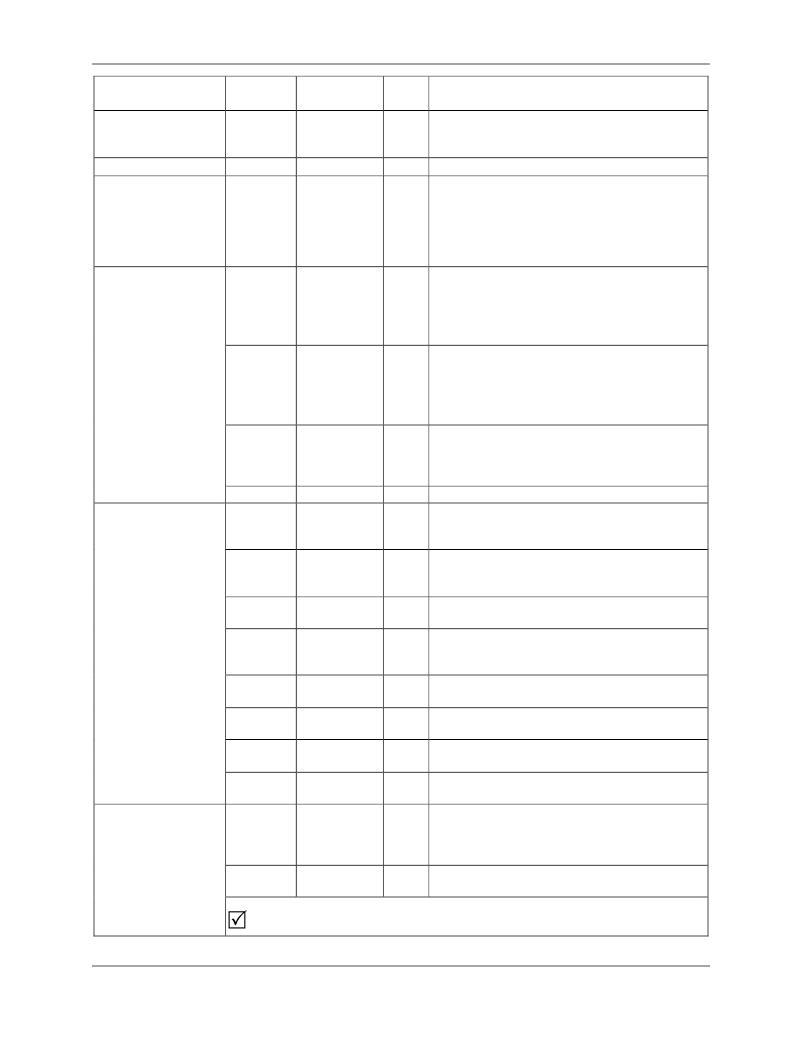

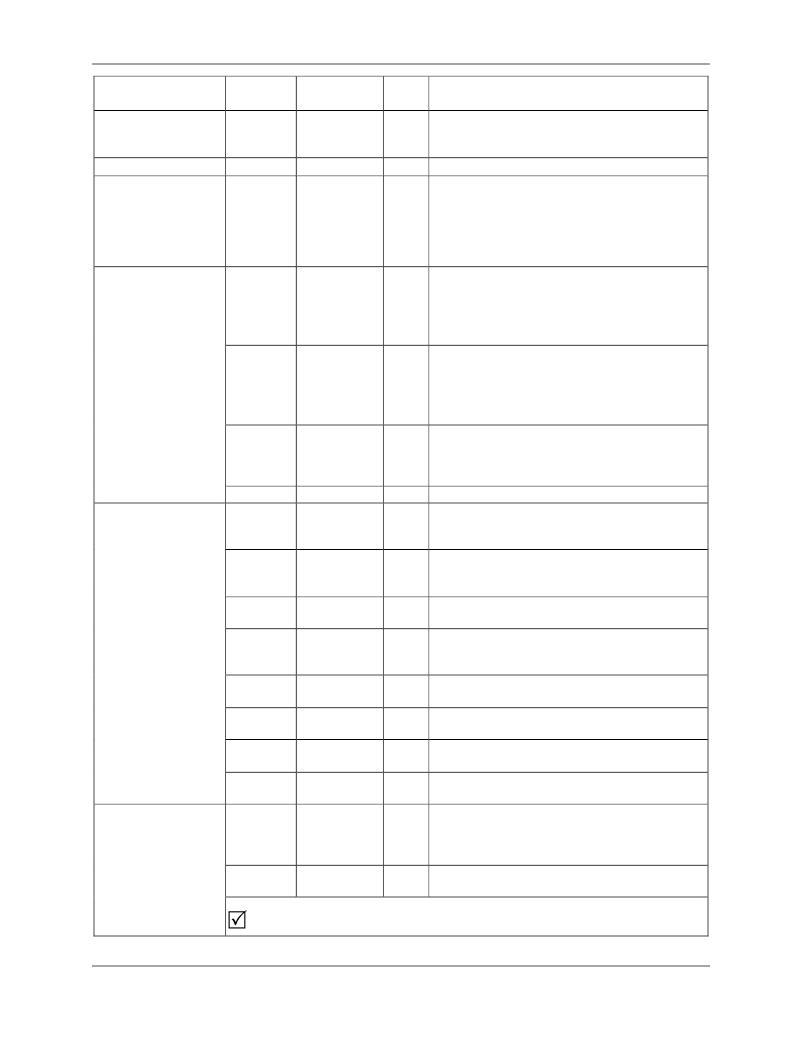

�Register�

�(Alternate� Name)�

�ERASE�

�(FLSH_ERASE)�

�FL_BANK�

�PGADDR�

�(FLSH_PGADR[5:0])�

�FLSHCRL�

�IFLAGS�

�INTBITS�

�(� INT0� …� INT6� )�

�SFR�

�Address�

�0x94�

�0xB6[2:0]�

�0xB7�

�0xB2[0]�

�0xB2[1]�

�0xB2[6]�

�0xB2[7]�

�0xE8[0]�

�0xE8[1]�

�0xE8[2]�

�0xE8[3]�

�0xE8[4]�

�0xE8[5]�

�0xE8[6]�

�0xE8[7]�

�0xF8[6:0]�

�0xF8[7]�

�Bit� Field�

�Name�

�FLSH_PWE�

�FLSH_MEEN�

�SECURE�

�PREBOOT�

�IE_XFER�

�IE_RTC�

�FWCOL1�

�FWCOL0�

�IE_PB�

�IE_WAKE�

�PLL_RISE�

�PLL_FALL�

�INT6� …� INT0�

�WD_RST�

�R/W�

�W�

�R/W�

�R/W�

�R/W�

�W�

�R/W�

�R�

�R/W�

�R/W�

�R/W�

�R/W�

�R/W�

�R/W�

�R/W�

�R/W�

�R�

�W�

�Description�

�This� register� is� used� to� initiate� either� the� Flash�

�Mass� Erase� cycle� or� the� Flash� Page� Erase� cycle.�

�See� the� Flash� Memory� section� for� details.�

�Flash� Bank� Selection.�

�Flash� Page� Erase� Address� register.� Contains�

�the� flash� memory� page� address� (page� 0� through�

�page� 127)� that� will� be� erased� during� the� Page�

�Erase� cycle� (default� =� 0x00).�

�Must� be� re-written� for� each� new� Page� Erase�

�cycle.�

�Program� Write� Enable:�

�0:� MOVX� commands� refer� to� XRAM�

�Space,� normal� operation� (default).�

�1:� MOVX� @DPTR,A� moves� A� to� Program�

�Space� (Flash)� @� DPTR.�

�Mass� Erase� Enable:�

�0:� Mass� Erase� disabled� (default).�

�1:� Mass� Erase� enabled.�

�Must� be� re-written� for� each� new� Mass� Erase�

�cycle.�

�Enables� security� provisions� that� prevent� external�

�reading� of� flash� memory� and� CE� program� RAM.�

�This� bit� is� reset� on� chip� reset� and� may� only� be�

�set.� Attempts� to� write� zero� are� ignored.�

�Indicates� that� the� preboot� sequence� is� active.�

�This� flag� monitors� the� XFER_BUSY� interrupt.�

�It� is� set� by� hardware� and� must� be� cleared� by�

�the� interrupt� handler.�

�This� flag� monitors� the� RTC_1SEC� interrupt.� It�

�is� set� by� the� hardware� and� must� be� cleared� by�

�the� interrupt� handler.�

�This� flag� indicates� that� a� flash� write� was� in�

�progress� while� the� CE� was� busy.�

�This� flag� indicates� that� a� flash� write� was�

�attempted� when� the� CE� was� attempting� to�

�begin� a� code� pass.�

�This� flag� indicates� that� the� wake-up� pushbutton�

�was� pressed.�

�This� flag� indicates� that� the� MPU� was� awakened�

�by� the� autowake� timer.�

�PLL_RISE� Interrupt� Flag:�

�Write� 0� to� clear� the� PLL_RISE� interrupt� flag.�

�PLL_FALL� Interrupt� Flag:�

�Write� 0� to� clear� the� PLL_FALL� interrupt� flag.�

�Interrupt� inputs.� The� MPU� may� read� these� bits�

�to� see� the� status� of� external� interrupts� INT0� up�

�to� INT6� .� These� bits� do� not� have� any� memory�

�and� are� primarily� intended� for� debug� use.�

�The� WDT� is� reset� when� a� 1� is� written� to� this�

�bit.�

�Only� byte� operations� on� the� entire� INTBITS� register� should� be� used� when�

�writing.� The� byte� must� have� all� bits� set� except� the� bits� that� are� to� be� cleared.�

�Rev� 2�

�25�

�相关PDF资料 |

PDF描述 |

|---|---|

| R1S12-1212/H | CONV DC/DC 1W 12VIN 12VOUT |

| VI-BNW-EU-F3 | CONVERTER MOD DC/DC 5.5V 200W |

| LM285MX-2.5/NOPB | IC VREF SHUNT 2.5V 8-SOIC |

| RCD-24-1.20/W | LED DRVR CONST 1.2A 3-33VOUT |

| 78M6618-M/F/P1 | IC PWR MEASUREMENT OCTAL 68QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6532F-IGTR/F | 功能描述:计量片上系统 - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6532F-IGTR/F1 | 功能描述:计量片上系统 - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6533 | 制造商:TERIDIAN 制造商全称:TERIDIAN 功能描述:Energy Meter IC |

| 71M6533-DB | 功能描述:开发板和工具包 - 8051 71M6533 Demo Brd RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

| 71M6533G | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Exceeds IEC 62053/ANSI C12.20 Standards |

发布紧急采购,3分钟左右您将得到回复。