- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6542G-IGTR/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | 71M6542G-IGTR/F |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 封装: | LEAD FREE, LQFP-100 |

| 文件页数: | 156/165页 |

| 文件大小: | 2208K |

| 代理商: | 71M6542G-IGTR/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页当前第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页

90

2008–2011 Teridian Semiconductor Corporation

v1.1

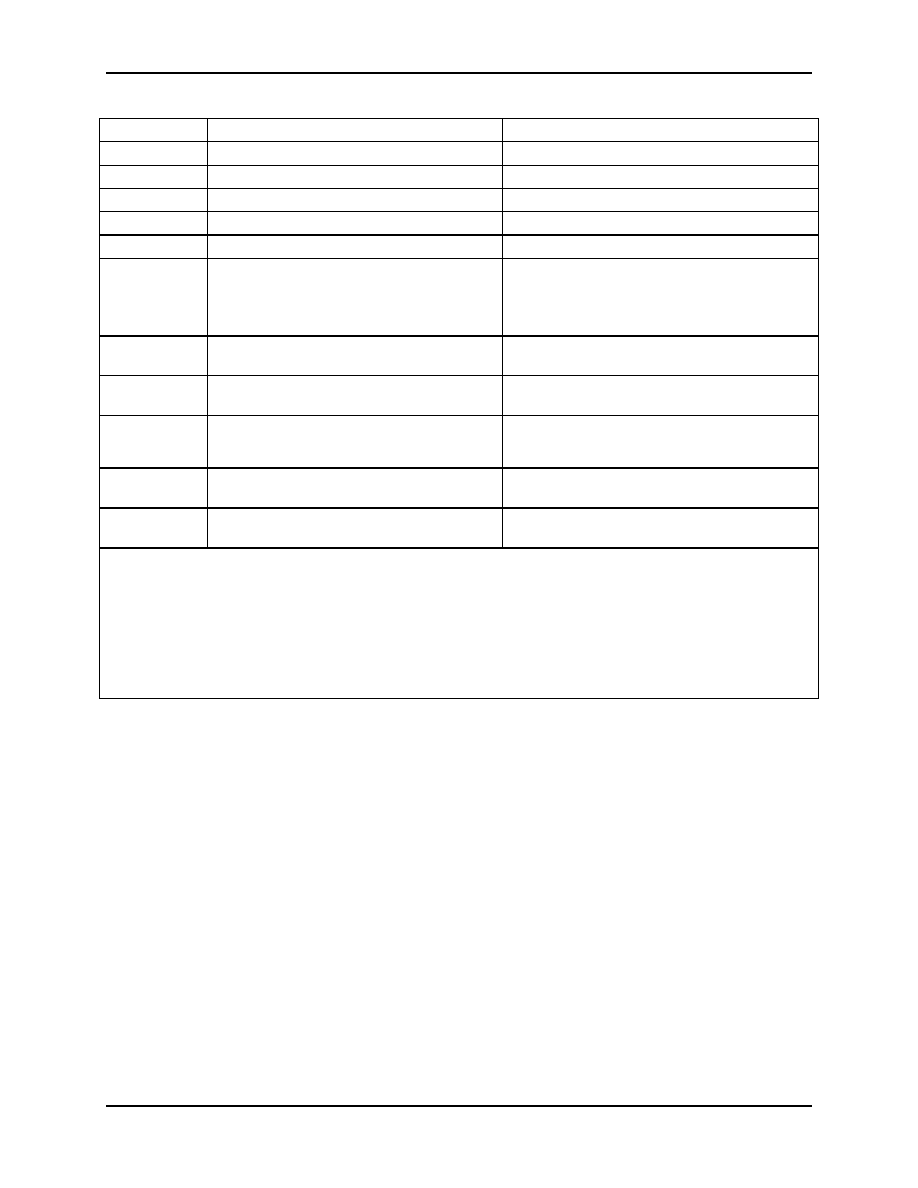

Table 71: Clear Events for WAKE flags

Flag

Wake on:

Clear Events

WF_TMR

Timer expiration

WAKE falls

WF_PB

PB pin high level

WAKE falls

WF_RX

Either edge RX pin

WAKE falls

WF_DIO4

SEGDIO4 rising edge

WAKE falls

WF_DIO52

SEGDIO52 high level (71M6542F only)

WAKE falls

WF_DIO55

If OPT_RXDIS = 1 (I/O RAM 0x2457[2]),

wake on SEGDIO55 high

If OPT_RXDIS = 0

wake on either edge of OPT_RX

WAKE falls

WF_RST

RESET pin driven high

WAKE falls, WF_CSTART, WF_RSTBIT,

WF_OVF, WF_BADVDD

WF_RSTBIT

RESET bit is set (I/O RAM 0x2200[3])

WAKE falls, WF_CSTART, WF_OVF,

WF_BADVDD, WF_RST

WF_ERST

E_RST pin driven high and the ICE

interface must be enabled by driving the

ICE_E pin high.

WAKE falls, WF_CSTART, WF_RST,

WF_OVF, WF_RSTBIT

WF_OVF

Watchdog (WD) reset

WAKE falls, WF_CSTART, WF_RSTBIT,

WF_BADVDD, WF_RST

WF_CSTART

Coldstart (i.e., after the application of first

power)

WAKE falls, WF_RSTBIT, WF_OVF,

WF_BADVDD, WF_RST

Note:

“WAKE falls” implies that the internal WAKE signal has been reset, which happens automatically upon

entry into LCD mode or SLEEP mode (i.e., when the MPU sets the LCD_ONLY bit (I/O RAM 0x28B2[6]) or

the SLEEP (I/O RAM 0x28B2[7]) bit). When the internal WAKE signal resets, all wake flags are reset.

Since the various wake flags are automatically reset when WAKE falls, it is not necessary for the MPU to

reset these flags before entering LCD mode or SLEEP mode. Also, other wake events can cause the

wake flag to reset, as indicated above (e.g., the WF_RST flag can also be reset by any of the following

flags setting: WF_CSTART, WS_RSTBIT, WF_OVF, WF_BADVDD)

3.4.2

Wake on Timer

If the part is in SLP or LCD mode, it can be awakened by the Wake Timer. Until this timer times out, the

MPU is in reset due to the internal WAKE signal being low. When the Wake Timer times out, WAKE rises

and within three CK32 cycles, the MPU begins to execute. The MPU can determine that the timer woke it

by checking the WF_TMR wake flag (I/O RAM 0x28B1[2]).

The Wake Timer begins timing when the part enters LCD or SLP mode. Its duration is controlled by the

value in the WAKE_TMR[7:0] register (I/O RAM 0x2880). The timer duration is WAKE_TMR +1 seconds.

The Wake Timer is armed by setting WAKE_ARM = 1 (I/O RAM 0x28B2[5]). It must be armed at least

three RTC cycles before either SLP or LCD modes are initiated. Setting WAKE_ARM presets the timer

with the value in WAKE_TMR and readies the timer to start when the MPU writes to the SLEEP (I/O RAM

0x28B2[7]) or LCD_ONLY (I/O RAM 0x28B2[6]) bits. The timer is neither reset nor disarmed when the

MPU wakes-up. Thus, once armed and set, the MPU continues to be awakened WAKE_TMR[7:0]

seconds after it requests SLP mode or LCD mode (i.e., once written, the WAKE_TMR[7:0] register holds

its value and does not have to be re-written each time the MPU enters SLP or LCD mode. Also, since

WAKE_TMR[7:0] is non-volatile, it also holds its value through resets and power failures).

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6541G-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6541F-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6541D-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| 71M6542F-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6541D-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6542GT-IGT/F | 制造商:Maxim Integrated Products 功能描述:1-PHASE, 128KB, PRES TEMP SENSOR - Bulk |

| 71M6542GT-IGTR/F | 制造商:Maxim Integrated Products 功能描述:1-PHASE, 128KB, PRES TEMP SENSOR - Tape and Reel |

| 71M6543F | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Selectable Gain of 1 or 8 for One Current Energy Meter ICs Metrology Compensation |

| 71M6543F-DB | 功能描述:开发板和工具包 - 8051 71M6543 Eval Kit RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

| 71M6543F-DB-CT | 功能描述:开发板和工具包 - 8051 71M6543 Eval Kit RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。