- 您现在的位置:买卖IC网 > PDF目录294128 > 72V845L15PFI8 (INTEGRATED DEVICE TECHNOLOGY INC) 4K X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 PDF资料下载

参数资料

| 型号: | 72V845L15PFI8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | FIFO |

| 英文描述: | 4K X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 |

| 封装: | TQFP-128 |

| 文件页数: | 11/26页 |

| 文件大小: | 325K |

| 代理商: | 72V845L15PFI8 |

IDT72V805/72V815/72V825/72V835/72V845

3.3 V CMOS DUAL SyncFIFO 256 x 18, 512 x 18, 1,024 x 18, 4,096 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

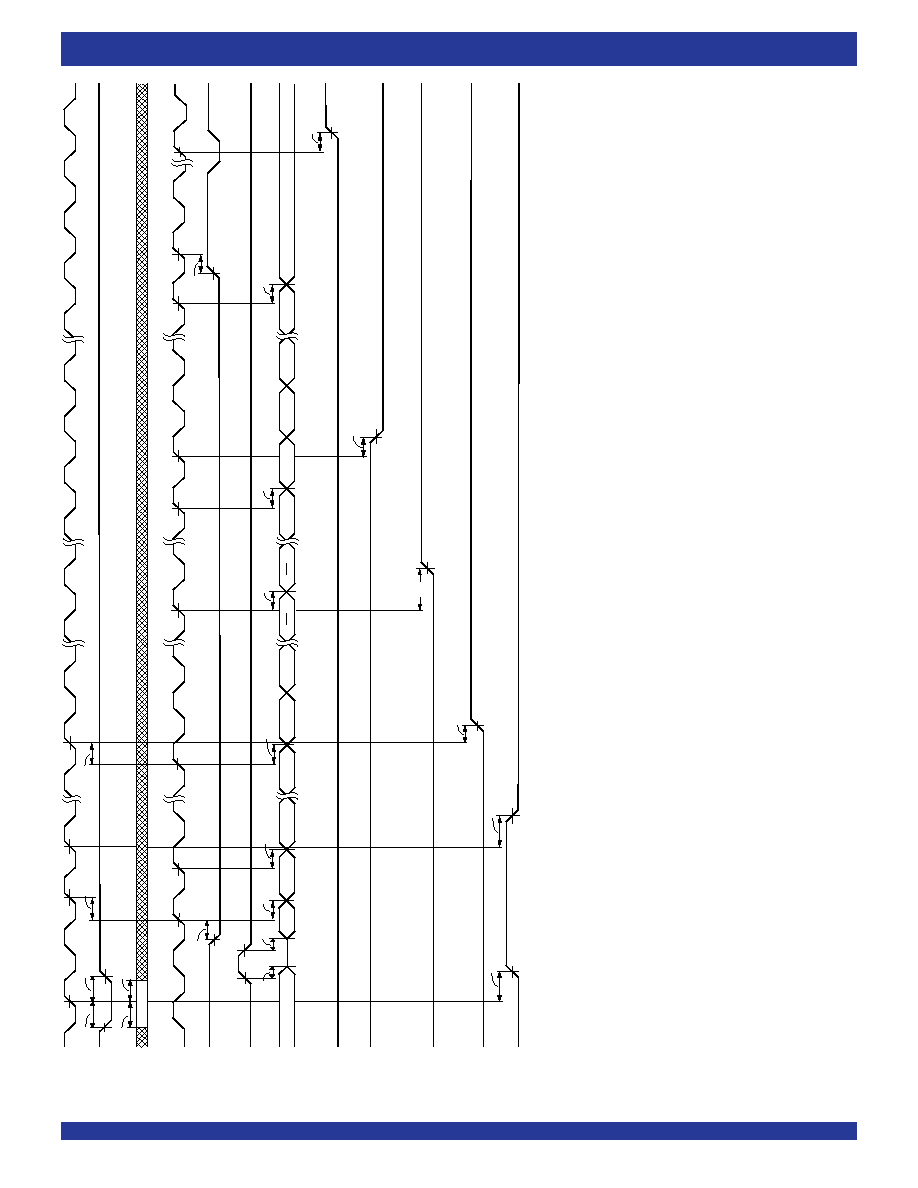

19

Figure

21.

Read

Timing

with

Synchronous

Programmable

Flags

(FWFT

Mode)

WCLK

12

WEN

D

0

-

D

17

RCLK

tENS

REN

Q

0

-Q

17

PAF

HF

PAE

IR

OR

W

1

W

1

W

2

W

3

W

m+2

W

[m+3]

tOHZ

tSKEW1

tENH

tDS

tDH

tOE

tA

tPAFS

tWFF

tENS

OE

tSKEW2

W

D

4295

drw

21

tPAES

W

[D-n]

W

[D-n-1]

tA

tHF

tREF

W

[D-1]

W

D

tA

W

[D-n+1]

W

[m+4]

W

[D-n+2]

(1)

(2)

1

tENS

D-1

+

1 ]

[

W

2

D-1

+

2 ]

[

W

2

NOTES:

1.

tSKEW1

is

the

minimum

time

between

a

rising

RCLK

edge

and

a

rising

WCLK

edge

to

guarantee

that

IR

will

go

LOW

after

one

WCLK

plus

t

WFF

.If

the

time

between

the

rising

edge

of

RLCK

and

the

rising

edge

of

WCLK

is

less

than

t

SKEW1

,then

the

IR

assertion

may

be

delayed

an

extra

WCLK

cycle.

2.

tSKEW2

is

the

minimum

time

between

a

rising

RCLK

edge

and

a

rising

WCLK

edge

for

PAF

to

go

HIGH

during

the

current

clock

cycle.

If

the

time

between

the

rising

edge

of

RCLK

and

the

rising

edge

of

WCLK

is

less

th

an

tSKEW2,

then

the

PAF

deassertion

time

may

be

delayed

an

extra

WCLK

cycle.

3.

LD

=

HIGH

4

.

n

=

PAE

offset,

m

=

PAF

offset,

D

=

maximum

FIFO

depth

=

257

words

for

the

IDT72V805,

513

words

for

the

IDT72V815,

1,025

words

for

the

IDT72V825,

2,04

9

words

for

IDT72V835

and

4,097

words

for

IDT72V845.

5

.

Select

this

mode

by

setting

(

FL

,

RXI

,

WXI

)=

(1,0,1)

during

Reset.

相关PDF资料 |

PDF描述 |

|---|---|

| 72V805L15PFI9 | 256 X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 |

| 72V805L15PF8 | 256 X 18 BI-DIRECTIONAL FIFO, 10 ns, PQFP128 |

| 7305-0-15-15-47-14-04-0 | BRASS, GOLD FINISH, PCB TERMINAL |

| 7305-0-15-15-47-01-04-0 | BRASS, GOLD FINISH, PCB TERMINAL |

| 7305-0-15-01-47-27-04-0 | BRASS, TIN FINISH, PCB TERMINAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 72V845L20PF | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72V845L20PF8 | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72V84L15PA | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

| 72V84L15PA8 | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Async Dual Depth/Width Bi-Dir 4K x 9 x 2 56-Pin TSSOP T/R 制造商:Integrated Device Technology Inc 功能描述:FIFO ASYNC DUAL DEPTH/WIDTH BI-DIR 4KX9X2 56TSSOP - Tape and Reel |

| 72V84L15PAG | 功能描述:先进先出 RoHS:否 制造商:IDT 电路数量: 数据总线宽度:18 bit 总线定向:Unidirectional 存储容量:4 Mbit 定时类型:Synchronous 组织:256 K x 18 最大时钟频率:100 MHz 访问时间:10 ns 电源电压-最大:3.6 V 电源电压-最小:6 V 最大工作电流:35 mA 最大工作温度:+ 85 C 封装 / 箱体:TQFP-80 封装: |

发布紧急采购,3分钟左右您将得到回复。