- 您现在的位置:买卖IC网 > PDF目录11007 > 73M1906B-IVT/F (Maxim Integrated Products)MICRODAA SET FXO OF VOIP 20TSSOP PDF资料下载

参数资料

| 型号: | 73M1906B-IVT/F |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 40/88页 |

| 文件大小: | 0K |

| 描述: | MICRODAA SET FXO OF VOIP 20TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 74 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

DS_1x66B_001

73M1866B/73M1966B Data Sheet

Rev. 1.6

45

8

PCM Highway Interface and Signal Processing

The PCM highway is the method by which the 73M1x66B exchanges PCM data with the host or other

PCM-enabled devices. The PCM data can be in either 8-bit compressed mode or in 16-bit linear mode.

Compression of the received signals from the PSTN line interface is selectable A-

law or μ-law, as

specified by ITU-T Recommendation G.711. The 73M1x66B is configurable with respect to tuning the

clock and time slot relationships. See Section 8.1 for details.

The PCM interface provided by the 73M1x66B consists of the following signals:

PCLK

The frequency at which bits are driven on the PCM highway. (Goes to the PCLKI pin.)

FS

PCM frame synchronization pulse.

DX

PCM data transmitted to the PCM highway.

DR

PCM data received from the PCM highway.

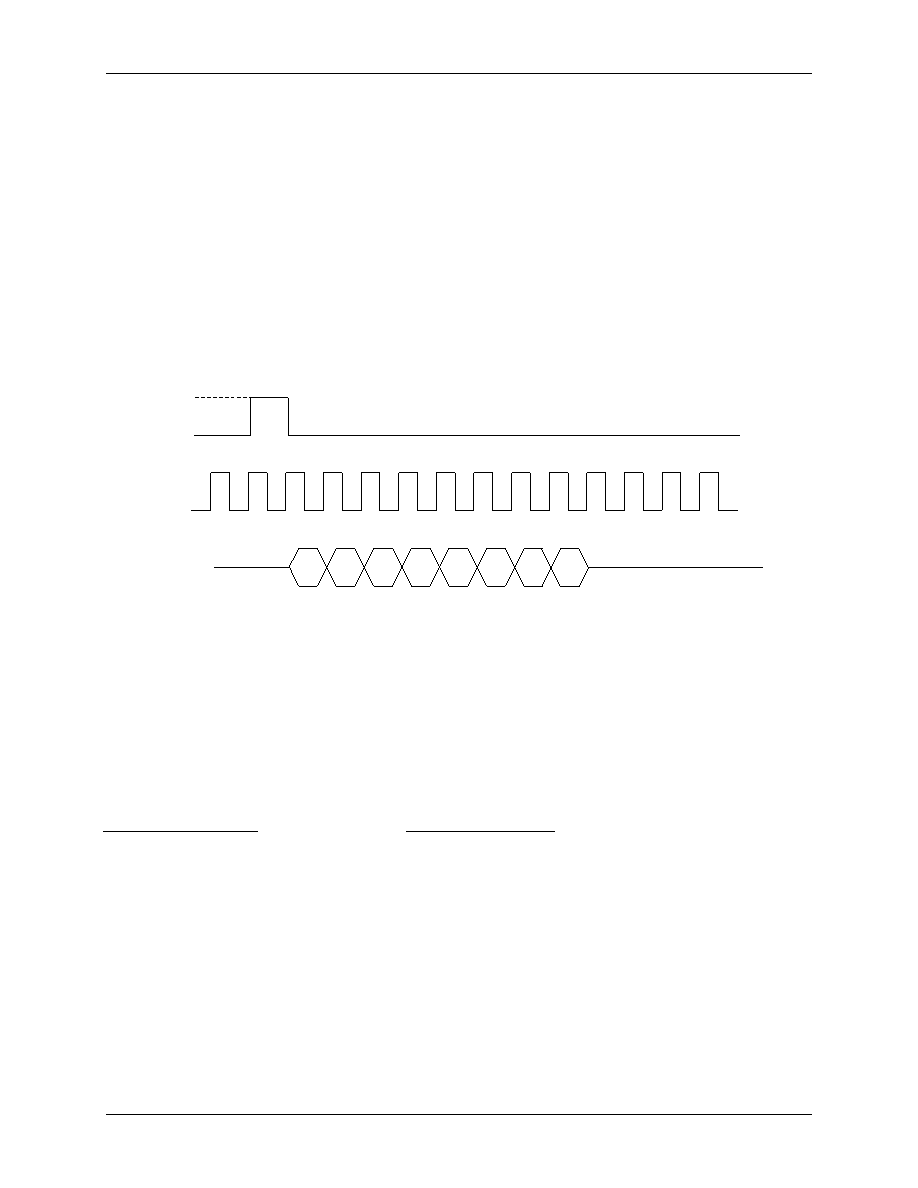

The basic timing relationship of PCM highway interface signals is shown in Figure 20.

FS

PCLK

DX

MSB

LSB

Figure 20: 8-bit Transmission Example

8.1

PCM Highway Interface Timing

Signal

FS defines the frame boundaries by being asserted at a rate of 8 kHz. The duration of FS is

defined by the setup and hold times around the falling edge of PCLK and can be extended to multiple

PCLK cycles. The timing relationship between

FS and PCLK is determined by the rising edge of FS and

the first falling edge of PCLK that follows the

FS rising edge. PCLK and FS are common to all devices

connected to the PCM highway. The ratio of PCLK frequency to

FS frequency determines the number of

bit slots available during a frame, i.e., the number of bits per frame. The number of bit slots divided by 8

is the number of 8-bit time slots available during the frame.

PCLK Frequency

= Bits per Frame

Bits per Frame

= Number of Time Slots per Frame

FS Frequency (8 kHz)

8-bits per Time Slot

Refined granularity to the time slot can be achieved by programming the clock slot offset. The clock slot

defines an offset in terms of the number of bits from the start of the time slot. The combination of the

transmit and receive time slot and clock slot registers determines the bit slot at which the 73M1x66B

begins transmitting or receiving a data sample. Adjustments of a half clock period can be made using

these controls in conjunction with TPOL and RPOL.

The 73M1x66B supports a 16-bit linear transmission and receive mode. The transmission and reception

of the data samples consumes two adjacent 8-bit time slots each on the PCM highway. The 16-bit data

sample is transmitted most significant bit first starting at the bit slot defined by the TTS and TCS controls.

The transmission lasts for 16 consecutive bit slots, as illustrated in Figure 21.

相关PDF资料 |

PDF描述 |

|---|---|

| 73M1916-IVT/F | MICRODAA SET FXO OF VOIP 20TSSOP |

| 73M1916-IVTR/F | MICRODAA SET FXO OF VOIP 20TSSOP |

| MC908QY4CDWER | IC MCU 8BIT 4K FLASH 16-SOIC |

| MC908QY4ACDWER | IC MCU 8BIT 4K FLASH 16-SOIC |

| S9S08SL8F1CTJ | IC MCU 8BIT 8KB FLASH 20TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 73M1906B-IVTR/F | 功能描述:电信线路管理 IC DAA-FXO VOLP System Host Side RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

| 73M1906-IVT/F | 制造商:TERIDIAN 功能描述: |

| 73M1912-IM/F | 功能描述:电信线路管理 IC MicroDAA Chip Set Line Side RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

| 73M1912-IMR/F | 功能描述:电信线路管理 IC MicroDAA Chip Set Line Side RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

| 73M1912-IVT/F | 功能描述:电信线路管理 IC MicroDAA Chip Set Line Side RoHS:否 制造商:STMicroelectronics 产品:PHY 接口类型:UART 电源电压-最大:18 V 电源电压-最小:8 V 电源电流:30 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:VFQFPN-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。