- 您现在的位置:买卖IC网 > PDF目录24830 > 935264570557 (NXP SEMICONDUCTORS) 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 PDF资料下载

参数资料

| 型号: | 935264570557 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 |

| 封装: | 12 X 12 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-315-1, LQFP-80 |

| 文件页数: | 4/36页 |

| 文件大小: | 145K |

| 代理商: | 935264570557 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

2000 Nov 17

12

Philips Semiconductors

Preliminary specication

1394 SBP-2 link layer controller

SAA7356HL

7.4.2

HITACHI H8 INTERFACE

In this mode, the address and data buses are

non-multiplexed. The address bus is connected directly to

the MICRO_ADDR pins and the data bus is connected

directly onto the MICRO_DATA pins.

The MICRO_CS pin must be asserted before the assertion

of the MICRO_READ pin. The SAA7356HL will stop

driving the microcontroller data bus when either the

MICRO_CS pin or the MICRO_READ pin are negated.

The H8 microcontroller supports wait states. The timing is

shown in Fig.6. Note that the MICRO_WAIT pin must be

low during the falling edge of the (H8) CLK during state T2.

Since the relationship between the SAA7356HL and the

H8 clock is unknown the MICRO_WAIT pin is asserted low

when the MICRO_READ and the MICRO_CS are

asserted. The SAA7356HL will de-assert the

MICRO_WAIT line once the data is ready for transfer.

7.4.3

NEC V851 INTERFACE SUPPORT

The most important timing information for this

microcontroller is given in Fig.7.

The MICRO_WAIT line must be low during the falling edge

of the (V851) CLK during state T2: this is the same

requirement as the H8. Instead of a MICRO_READ and a

MICRO_WRITE signal the V851 uses a R/W and DSTB

signal. The address lines are time multiplexed and should

be latched using the ASTB signal.

7.5

Interrupt handling

The SAA7356HL may use interrupts to communicate with

the microcontroller. The microcontroller will read from the

CmdToMicro register to find the interrupt reason.

If parameters are required with the command then this is

implied in the command byte.These parameters may then

be read from the SAA7356HL RAM using the RAM.Offset

and the RAM.Next registers.

7.6

Address map for the SAA7356HL

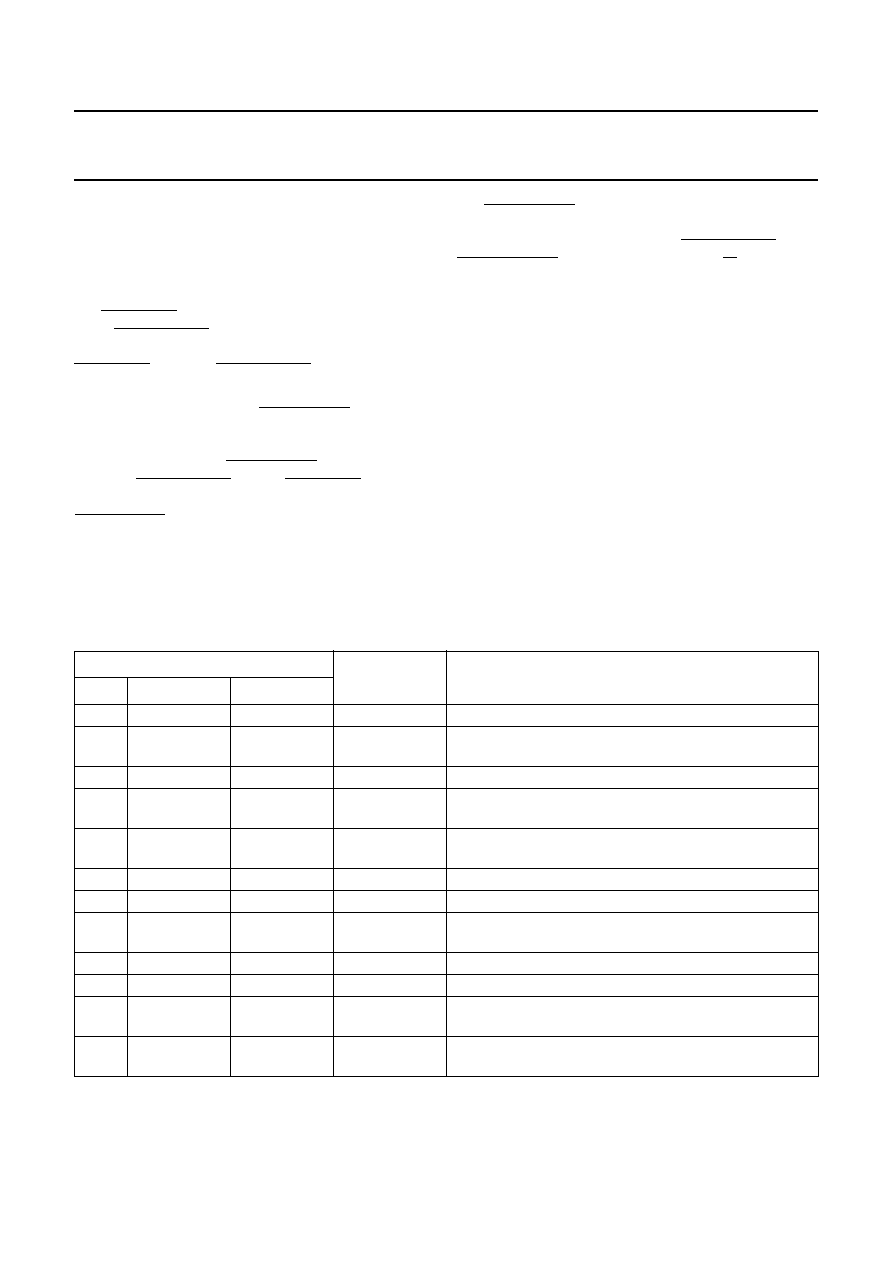

The address mapping for the 4-bit, 8-bit and 16-bit

addressing modes is given in Table 1.

Table 1

Big-endian register map for the SAA7356HL

ADDRESS

MNEMONIC

COMMENT

4-BIT

8-BIT

16-BIT

0

9C

FF90

Reserved

reserved

1

9D

FF91

InterruptEnable

enables the InterruptReason to assert the

microcontroller interrupt line

2

9E

FF92

InterruptReason provides the interrupt sources

3

9F

FF93

CmdFromMicro

command byte channel from the microcontroller to the

SAA7356HL

4

BC

FFB0

CmdToMicro

command byte from the SAA7356HL to the

microcontroller

5

BD

FFB1

Sbp2Start

used to complete the SAA7356HL initialization sequence

6

BE

FFB2

InterruptSet

allows setting of the ags in the InterruptReason register

7 to B

BF, DC to DF

FFB3,

FFD0 to FFD3

Reserved

reserved

C

FC

FFF0

RAM.OffsetB

High-byte of the offset address

D

FD

FFF1

RAM.OffsetA

Low-byte for the offset address

E

FE

FFF2

RAM.Next

RAM access register: forces a post-increment of the

RAM.Offset address

F

FF

FFF3

RAM.Current

RAM access register: no modication to the RAM.Offset

address

相关PDF资料 |

PDF描述 |

|---|---|

| 0803-7700-02 | Integrated VDSL Filter/Hybrid Solution |

| 935269451118 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 935269451112 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 0803-7700-03 | VDSL / PSTN CO Splitter |

| 935269471115 | 2.8 V FIXED POSITIVE LDO REGULATOR, 0.06 V DROPOUT, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

发布紧急采购,3分钟左右您将得到回复。