- 您现在的位置:买卖IC网 > PDF目录24830 > 935264570557 (NXP SEMICONDUCTORS) 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 PDF资料下载

参数资料

| 型号: | 935264570557 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), SERIAL COMM CONTROLLER, PQFP80 |

| 封装: | 12 X 12 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-315-1, LQFP-80 |

| 文件页数: | 7/36页 |

| 文件大小: | 145K |

| 代理商: | 935264570557 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

2000 Nov 17

15

Philips Semiconductors

Preliminary specication

1394 SBP-2 link layer controller

SAA7356HL

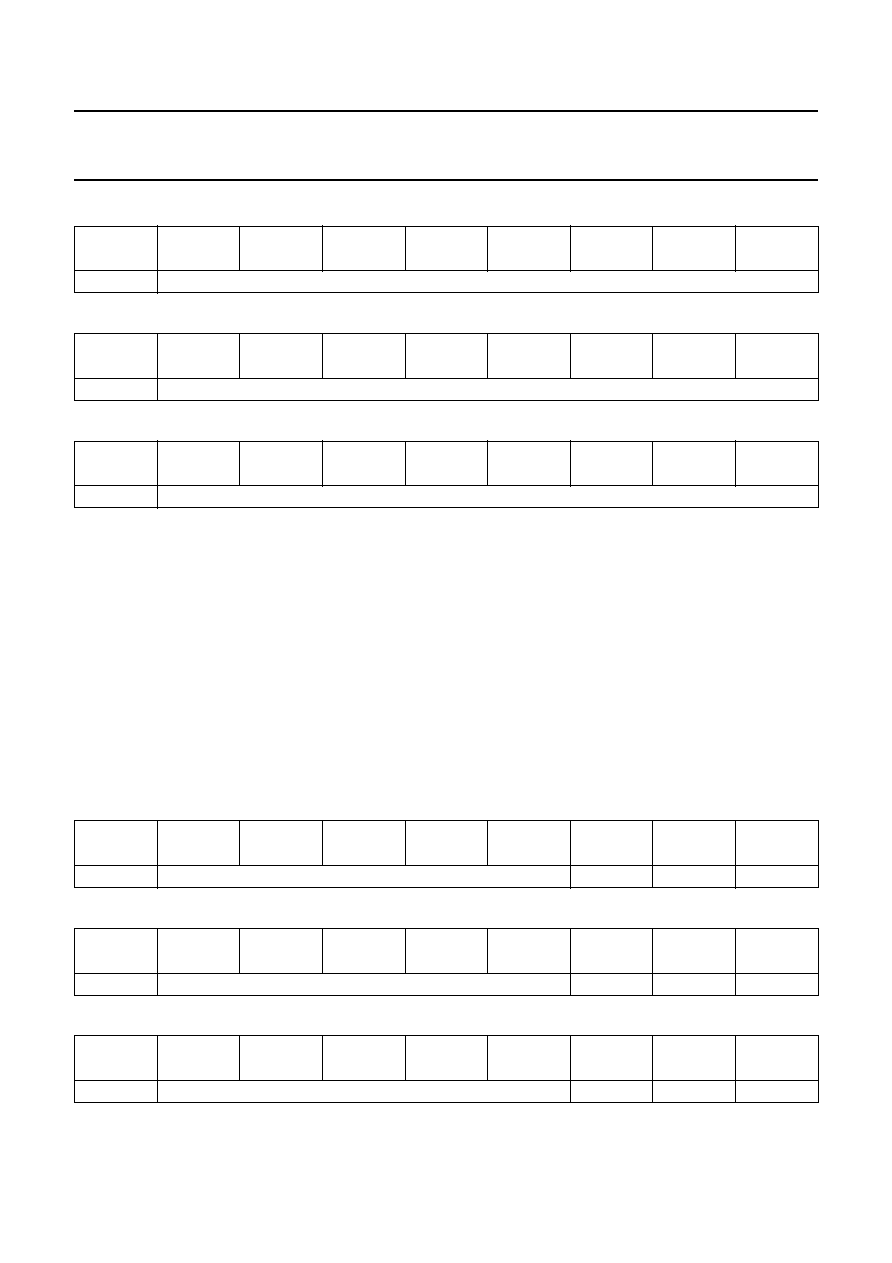

Table 2

CmdFromMicro register denition (read/write)

Table 3

Sbp2Start register denition (read/write)

Table 4

CmdToMicro register denition (read/write)

BYTE

NUMBER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

Command(7:0)

BYTE

NUMBER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

Command(7:0)

BYTE

NUMBER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

Command(7:0)

8.3

Interrupt registers

As mentioned in the previous section, the communications

may be interrupt driven. To facilitate this there is one

InterruptReason and one InterruptEnable register. The

interrupt to the microcontroller is of the AND-OR type and

is asserted when any of the maskable interrupts are

enabled and active: to enable an interrupt, the

corresponding field in the InterruptEnable register must

be set to logic 1. Reading from the InterruptReason

register provides the un-masked value: this allows polling

if desired.

The InterruptEnable and InterruptReason register

definitions are shown in Tables 5 and 6 respectively.

In addition to these two registers, the microcontroller may

set the values in the InterruptReason register: this may

be used for setting initial conditions, for example. To set

the required bits, a logic 1 must be written to the flag

location in the InterruptSet register: writing a logic 0 to

any bit-field has no effect. The InterruptSet register

definition is given in Table 7.

It is recommended that only the InterruptReason.CmdClr

flag is set as InterruptReason.CmdMicro will cause a

maskable interrupt to be asserted to the microcontroller.

The definition of the InterruptReason, InterruptEnable

and the InterruptSet register fields are shown in Table 8.

Table 5

InterruptEnable register denition (read/write)

Table 6

InterruptReason register denition (read/write)

Table 7

InterruptSet register denition (write only, read via InteruptReason)

BYTE

NUMBER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

Reserved

CmdMicro

BusReset

CmdClr

BYTE

NUMBER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

Reserved

CmdMicro

BusReset

CmdClr

BYTE

NUMBER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

Reserved

CmdMicro

Reserved

CmdClr

相关PDF资料 |

PDF描述 |

|---|---|

| 0803-7700-02 | Integrated VDSL Filter/Hybrid Solution |

| 935269451118 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 935269451112 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 0803-7700-03 | VDSL / PSTN CO Splitter |

| 935269471115 | 2.8 V FIXED POSITIVE LDO REGULATOR, 0.06 V DROPOUT, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

发布紧急采购,3分钟左右您将得到回复。