- 您现在的位置:买卖IC网 > PDF目录122717 > 954201BFLFT (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 954201BFLFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封装: | 0.300 INCH, 0.025 INCH PITCH, GREEN, MO-118, SSOP-56 |

| 文件页数: | 14/20页 |

| 文件大小: | 219K |

| 代理商: | 954201BFLFT |

3

Integrated

Circuit

Systems, Inc.

ICS954201

0819H—02/17/06

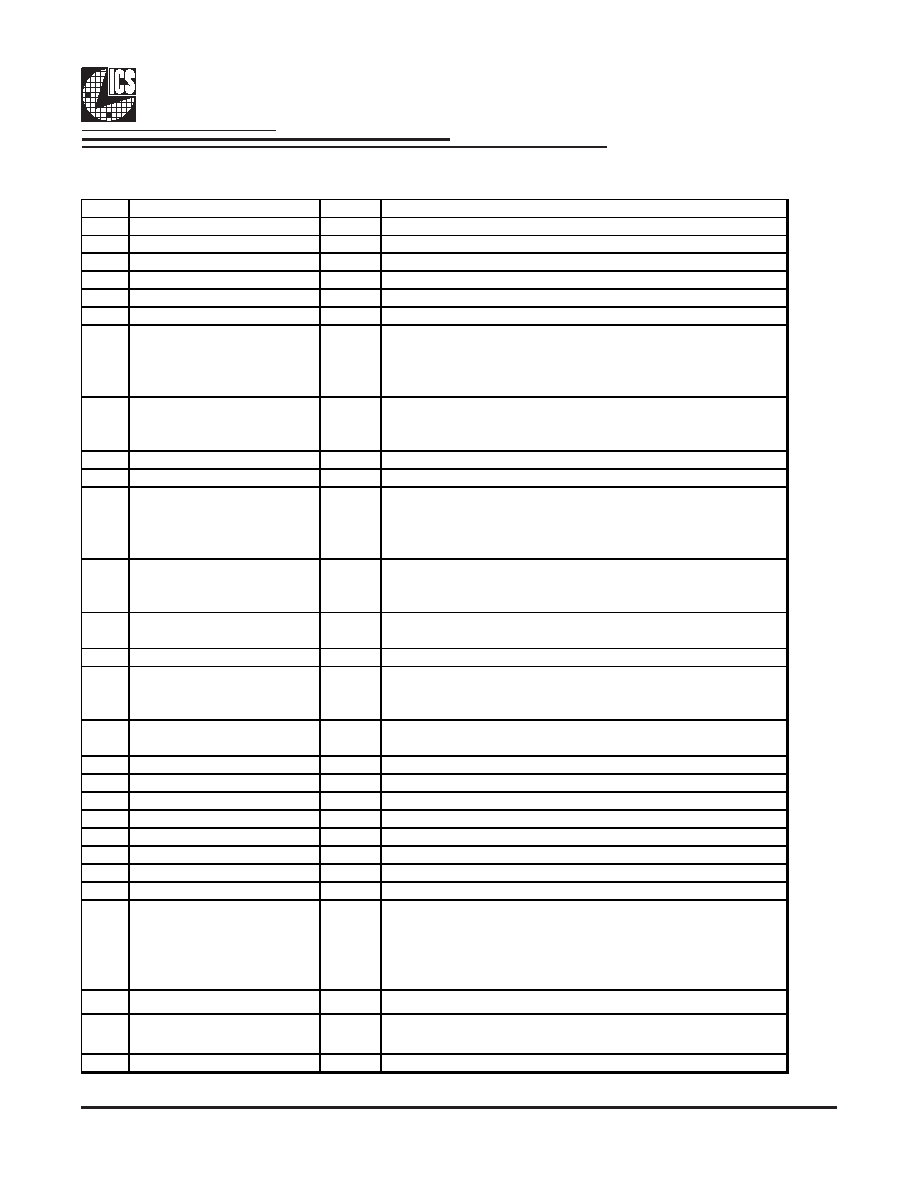

Pin Description (Continued)

PIN # PIN NAME

TYPE

DESCRIPTION

29

GND

PWR

Ground pin.

30

SRCCLKC5

OUT

Complement clock of differential SRC clock pair.

31

SRCCLKT5

OUT

True clock of differential SRC clock pair.

32

SRCCLKC6

OUT

Complement clock of differential SRC clock pair.

33

SRCCLKT6

OUT

True clock of differential SRC clock pair.

34

VDDSRC

PWR

Supply for SRC clocks, 3.3V nominal

35

CPUCLKC2_ITP/SRCCLKC7

OUT

Complimentary clock of CPU_ITP/SRC differential pair

CPU_ITP/SRC output. These are current mode outputs.

External resistors are required for voltage bias. Selected by

ITP_EN input.

36

CPUCLKT2_ITP/SRCCLKT7

OUT

True clock of CPU_ITP/SRC differential pair CPU_ITP/SRC

output. These are current mode outputs. External resistors are

required for voltage bias. Selected by ITP_EN input.

37

VDDA

PWR

3.3V power for the PLL core.

38

GNDA

PWR

Ground pin for the PLL core.

39

IREF

OUT

This pin establishes the reference current for the differential

current-mode output pairs. This pin requires a fixed precision

resistor tied to ground in order to establish the appropriate

current. 475 ohms is the standard value.

40

CPUCLKC1

OUT

Complimentary clock of differential pair CPU outputs. These are

current mode outputs. External resistors are required for voltage

bias.

41

CPUCLKT1

OUT

True clock of differential pair CPU outputs. These are current

mode outputs. External resistors are required for voltage bias.

42

VDDCPU

PWR

Supply for CPU clocks, 3.3V nominal

43

CPUCLKC0

OUT

Complimentary clock of differential pair CPU outputs. These are

current mode outputs. External resistors are required for voltage

bias.

44

CPUCLKT0

OUT

True clock of differential pair CPU outputs. These are current

mode outputs. External resistors are required for voltage bias.

45

GND

PWR

Ground pin.

46

SCLK

IN

Clock pin of SMBus circuitry, 5V tolerant.

47

SDATA

I/O

Data pin for SMBus circuitry, 5V tolerant.

48

VDDREF

PWR

Ref, XTAL power supply, nominal 3.3V

49

X2

OUT

Crystal output, Nominally 14.318MHz

50

X1

IN

Crystal input, Nominally 14.318MHz.

51

GND

PWR

Ground pin.

52

REFOUT

OUT

Reference Clock output

53

FS_C/TEST_SEL

IN

3.3V tolerant input for CPU frequency selection. Low voltage

threshold inputs, see input electrical characteristics for Vil_FS

and Vih_FS values.

TEST_Sel: 3-level latched input to enable test mode.

Refer to Test Clarification Table

54

CPU_STOP#

IN

Stops all CPUCLK, except those set to be free running clocks

55

PCI/SRC_STOP#

IN

Stops all PCICLKs and SRCCLKs besides the free-running

clocks at logic 0 level, when input low

56

PCICLK2

OUT

PCI clock output.

相关PDF资料 |

PDF描述 |

|---|---|

| 935271490512 | 4 CHANNEL(S), 5M bps, SERIAL COMM CONTROLLER, PQCC68 |

| 935271979118 | 8 I/O, PIA-GENERAL PURPOSE, PQCC16 |

| 935263358512 | 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PDSO20 |

| 9UMS9633BKLFT | 166.67 MHz, OTHER CLOCK GENERATOR, PQCC48 |

| 935263686518 | 6 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 954201BGLF | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 954201BGLFT | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| 954201BGLN | 制造商:Integrated Device Technology Inc 功能描述:PROGRAMMABLE PLL CLOCK SYNTHESIZER DUAL 56TSSOP - Rail/Tube |

| 954201BGLNT | 制造商:Integrated Device Technology Inc 功能描述:954201BGLNT - Tape and Reel |

| 954204BGLF | 制造商:Integrated Device Technology Inc 功能描述:56 TSSOP (LEAD FREE) - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。