- 您现在的位置:买卖IC网 > PDF目录25566 > 9FG1200DG-1LF (INTEGRATED DEVICE TECHNOLOGY INC) 400 MHz, OTHER CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | 9FG1200DG-1LF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 400 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| 封装: | 0.240 INCH, 0.020 INCH PITCH, ROHS COMPLIANT, MO-153, TSSOP-56 |

| 文件页数: | 23/23页 |

| 文件大小: | 188K |

| 代理商: | 9FG1200DG-1LF |

IDT

Frequency Gearing Clock for CPU, PCIe Gen1, Gen2 & FBD

1138C

02/08/10

ICS9FG1200D-1

9

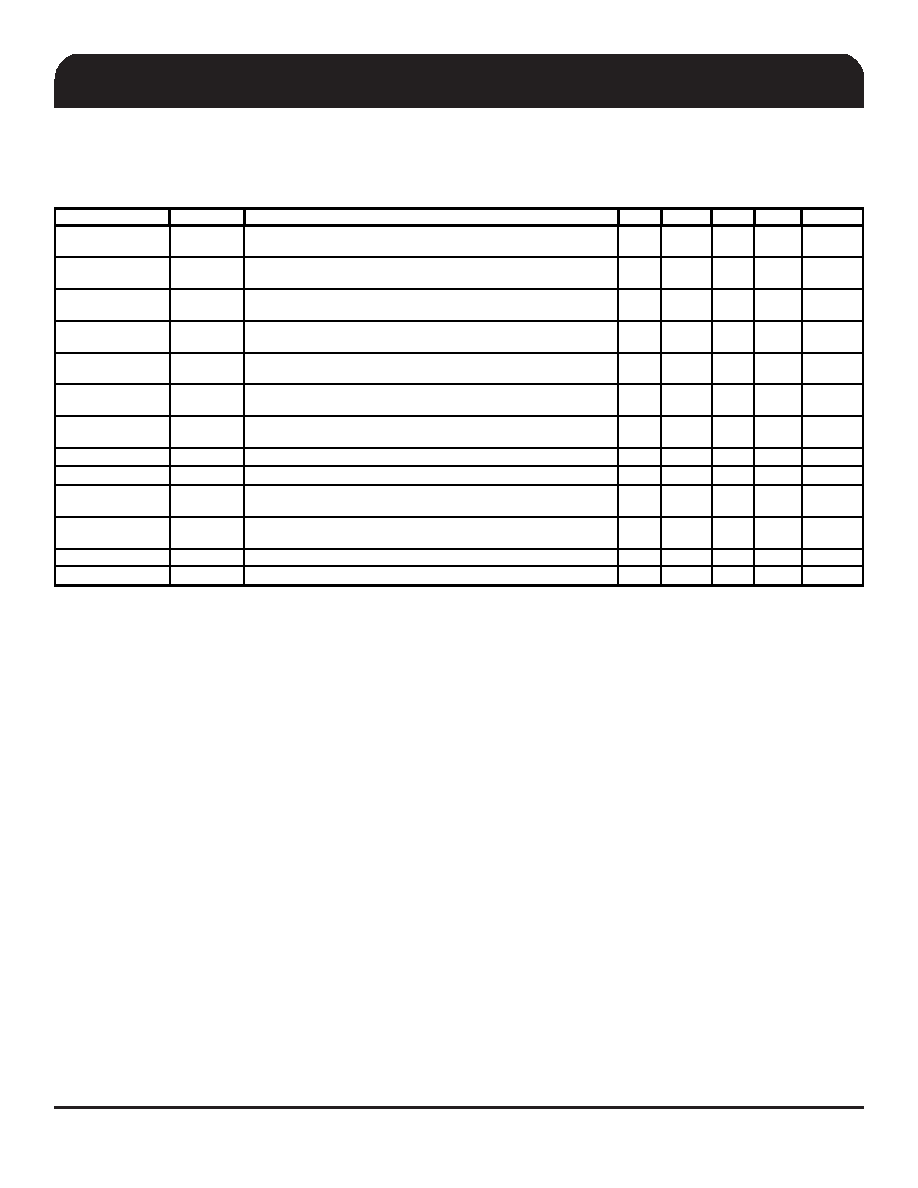

Electrical Characteristics - Skew and Differential Jitter Parameters

TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%

Group

Parameter

Description

Min

Typ

Max

Units

Notes

CLK_IN, DIF[x:0]

tSPO_PLL

Input-to-Output Skew in PLL mode (1:1 only),

nominal value @ 25°C, 3.3V

-500

140

500

ps

1,2,4,5,8,

12

CLK_IN, DIF[x:0]

tPD_BYP

Input-to-Output Skew in Bypass mode (1:1 only),

nominal value @ 25°C, 3.3V

2.5

3.1

4.5

ns

1,2,3,5,

12

CLK_IN, DIF [x:0]

ΔtSPO_PLL

Input-to-Output Skew Variation in PLL mode

(over specified voltage / temperature operating ranges)

270

|350|

ps

1,2,4,5,6,

10,12

CLK_IN, DIF [x:0]

ΔtPD_BYP

Input-to-Output Skew Variation in Bypass mode

(over specified voltage / temperature operating ranges)

470

|500|

ps

1,2,3,4,5,

6,10,12

DIF[11:10]

tSKEW_G2

Output-to-Output Skew Group of 2

(Common to Bypass and PLL mode)

10

25

ps

1,2,12

DIF[9:0]

tSKEW_G10

Output-to-Output Skew Group of 10

(Common to Bypass and PLL mode)

40

50

ps

1,2,12

DIF[11:0]

tSKEW_A12

Output-to-Output Skew across all 12 outputs (Common to

Bypass and PLL mode - all outputs at same gear)

80

100

ps

1,2,3,12

DIF[11:0]

tJPH

Differential Phase Jitter (RMS Value)

5

10

ps

1,4,7,12

DIF[11:0]

tSSTERROR

Differential Spread Spectrum Tracking Error (peak to peak)

40

80

ps

1,4,9,12

PLL Jitter Peaking

jpeak-hibw

(HIGH_BW# = 0)

0

2.15

2.5

dB

11,12

PLL Jitter Peaking

jpeak-lobw

(HIGH_BW# = 1)

0

1.2

2

dB

11,12

PLL Bandwidth

pllHIBW

(HIGH_BW# = 0)

2

3.6

4

MHz

12,13

PLL Bandwidth

pllLOBW

(HIGH_BW# = 1)

0.7

1.2

1.4

MHz

12,13

NOTES on Skew and Differential Jitter Parameters:

8. t is the period of the input clock

11.

Measured as maximum pass band gain. At frequencies within the loop BW, highest point of magnification is called PLL jitter peaking.

12. Guaranteed by design and characterization, not 100% tested in production.

13.

Measured at 3 db down or half power point.

1. Measured into fixed 2 pF load cap. Input to output skew is measured at the first output edge following the corresponding input.

2. Measured from differential cross-point to differential cross-point

10. This parameter is an absolute value. It is not a double-sided figure.

9. Differential spread spectrum tracking error is the difference in spread spectrum tracking between two 9FG1200D-1 devices This parameter is measured at the outputs of two

separate 9FG1200D-1 devices driven by a single CK410B+ in Spread Spectrum mode. The 9FG1200D-1 must set to high bandwidth. The spread spectrum characterisitics are

: maximum of 0.5%, 30 to 33KHz modulation frequency, linear profile.

5. Measured with scope averaging on to find mean value.

6. Long-term variation from nominal of input-to-output skew over temperature and voltage for a single device.

7. This parameter is measured at the outputs of two separate 9FG1200D-1 devices driven by a single CK410B+. The 9FG1200D-1 must be set to high bandwidth. Differential

phase jitter is the accumulation of the phase jitter not shared by the outputs (eg. not including the affects of spread spectrum). Target ranges of consideration are agents with

BW of 1-22MHz and 11-33MHz.

3. All Bypass Mode Input-to-Output specs refer to the timing between an input edge and the specific output edge created by it.

4. This parameter is deterministic for a given device

相关PDF资料 |

PDF描述 |

|---|---|

| 9FG1200DF-1LF | 400 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| 9FG1200YG-1LF-T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9FG1200YF-1LF-T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9FG1201HGLF-T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9FG1201HGLF | 400 MHz, OTHER CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 9FG1200DG-1LFT | 功能描述:时钟缓冲器 RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9FG1201CGLF | 制造商:INT_CIR_SYS 功能描述: |

| 9FG1201CGLFT | 功能描述:IC CLOCK MANANGEMENT 制造商:idt, integrated device technology inc 系列:* 零件状态:最後搶購 标准包装:1,000 |

| 9FG1201HFLF | 功能描述:时钟缓冲器 12 Output PCIe Gearng Buffer RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| 9FG1201HFLFT | 功能描述:时钟缓冲器 12 Output PCIe Gearng Buffer RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。