- 您现在的位置:买卖IC网 > PDF目录294782 > A1280A-1CQG172M FPGA, 1232 CLBS, 8000 GATES, 60 MHz, CQFP172 PDF资料下载

参数资料

| 型号: | A1280A-1CQG172M |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1232 CLBS, 8000 GATES, 60 MHz, CQFP172 |

| 封装: | CERAMIC, CQFP-172 |

| 文件页数: | 24/54页 |

| 文件大小: | 333K |

| 代理商: | A1280A-1CQG172M |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

RadTolerant FPGAs

1- 26

v3.1

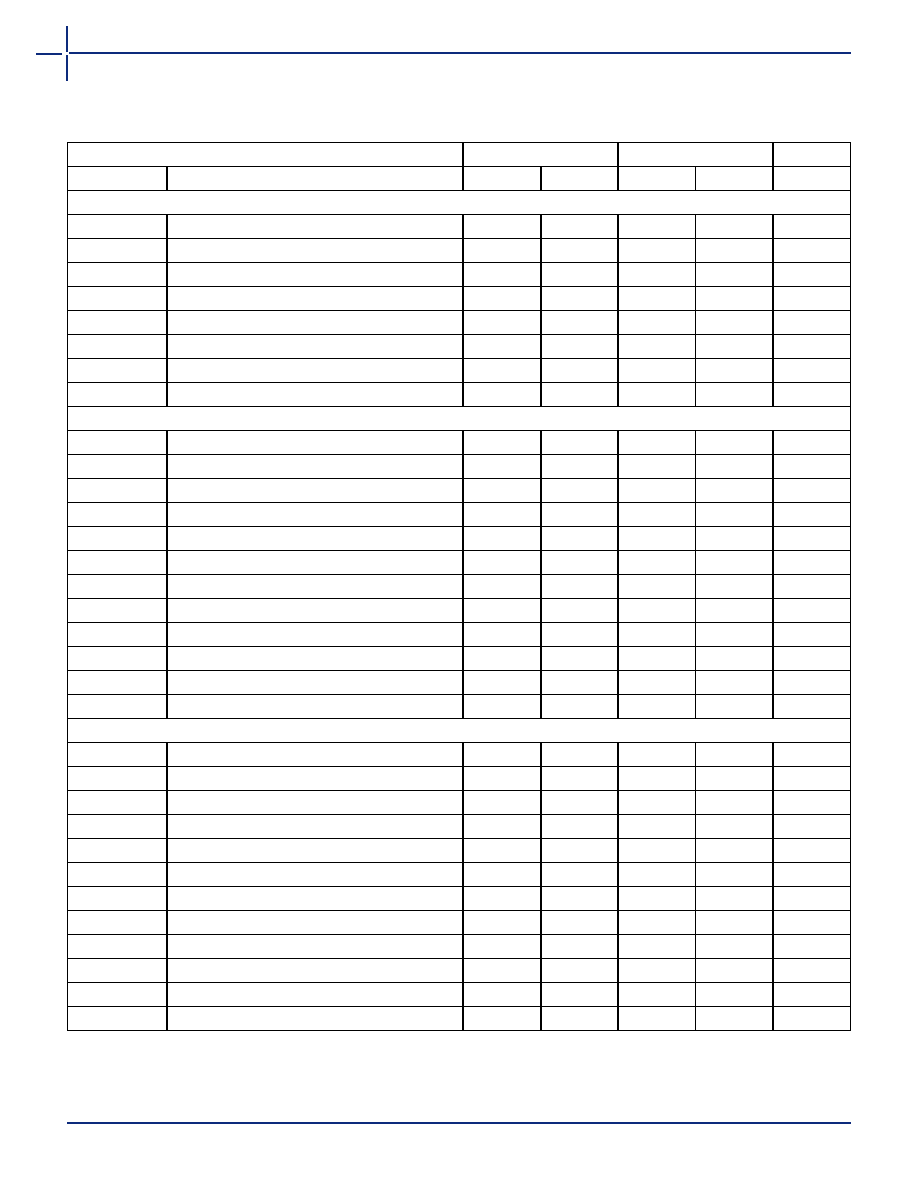

Table 1-19 RT1460A, A1460A I/O and Output Modules

Worst-Case Military Conditions, VCC = 4.5 V, TJ = 125°C

–1 Speed

Std Speed

Parameter

Description

Min.

Max.

Min.

Max.

Units

I/O Module Sequential Timing

tINH

Input F-F Data Hold (w.r.t. IOCLK Pad)

0.0

ns

tINSU

Input F-F Data Setup (w.r.t. IOCLK Pad)

2.1

2.4

ns

tIDEH

Input Data Enable Hold (w.r.t. IOCLK Pad)

0.0

ns

tIDESU

Input Data Enable Setup (w.r.t. IOCLK Pad)

8.7

10.0

ns

tOUTH

Output F-F Data Hold (w.r.t. IOCLK Pad)

1.1

1.2

ns

tOUTSU

Output F-F Data Setup (w.r.t. IOCLK Pad)

1.1

1.2

ns

tODEH

Output Data Enable Hold (w.r.t. IOCLK Pad)

0.5

0.6

ns

tODESU

Output Data Enable Setup (w.r.t. IOCLK Pad)

2.0

2.4

ns

TTL Output Module Timing1

tDHS

Data to Pad, High Slew

7.5

8.9

ns

tDLS

Data to Pad, Low Slew

11.9

14.0

ns

tENZHS

Enable to Pad, Z to H/L, High Slew

6.0

7.0

ns

tENZLS

Enable to Pad, Z to H/L, Low Slew

10.9

12.8

ns

tENHSZ

Enable to Pad, H/L to Z, High Slew

11.5

13.5

ns

tENLSZ

Enable to Pad, H/L to Z, Low Slew

10.9

12.8

ns

tCKHS

IOCLK Pad to Pad H/L, High Slew

11.6

13.4

ns

tCKLS

IOCLK Pad to Pad H/L, Low Slew

17.8

19.8

ns

dTLHHS

Delta Low to High, High Slew

0.04

ns/pF

dTLHLS

Delta Low to High, Low Slew

0.07

0.08

ns/pF

dTHLHS

Delta High to Low, High Slew

0.05

0.06

ns/pF

dTHLLS

Delta High to Low, Low Slew

0.07

0.08

ns/pF

CMOS Output Module Timing1

tDHS

Data to Pad, High Slew

9.2

10.8

ns

tDLS

Data to Pad, Low Slew

17.3

20.3

ns

tENZHS

Enable to Pad, Z to H/L, High Slew

7.7

9.1

ns

tENZLS

Enable to Pad, Z to H/L, Low Slew

13.1

15.5

ns

tENHSZ

Enable to Pad, H/L to Z, High Slew

10.9

12.8

ns

tENLSZ

Enable to Pad, H/L to Z, Low Slew

10.9

12.8

ns

tCKHS

IOCLK Pad to Pad H/L, High Slew

14.1

16.0

ns

tCKLS

IOCLK Pad to Pad H/L, Low Slew

20.2

22.4

ns

dTLHHS

Delta Low to High, High Slew

0.06

0.07

ns/pF

dTLHLS

Delta Low to High, Low Slew

0.11

0.13

ns/pF

dTHLHS

Delta High to Low, High Slew

0.04

0.05

ns/pF

dTHLLS

Delta High to Low, Low Slew

0.05

0.06

ns/pF

Note:

1. Delays based on 35pF loading.

相关PDF资料 |

PDF描述 |

|---|---|

| A1280A-CQG172B | FPGA, 1232 CLBS, 8000 GATES, 41 MHz, CQFP172 |

| A1280A-CQG172M | FPGA, 1232 CLBS, 8000 GATES, 41 MHz, CQFP172 |

| A1020B-CQ84C | FPGA, 547 CLBS, 2000 GATES, 37 MHz, CQFP84 |

| A14100A-1CQ256B | FPGA, 1377 CLBS, 30000 GATES, 100 MHz, CQFP256 |

| A1280A-1CQ172E | FPGA, 1232 CLBS, 8000 GATES, 60 MHz, CQFP172 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A1280A-1CQG176B | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1280A-1CQG176C | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1280A-1CQG176I | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1280A-1CQG176M | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

| A1280A-1PG160B | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ACT 2 Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。