- 您现在的位置:买卖IC网 > PDF目录8610 > AD5734RBREZ-REEL7 (Analog Devices Inc)IC DAC 14BIT DSP/SRL 24TSSOP PDF资料下载

参数资料

| 型号: | AD5734RBREZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 22/32页 |

| 文件大小: | 0K |

| 描述: | IC DAC 14BIT DSP/SRL 24TSSOP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 设计资源: | Software Configurable 14-Bit Quad-Channel Unipolar/Bipolar Voltage Output Using AD5734R (CN0084) |

| 标准包装: | 1,000 |

| 设置时间: | 10µs |

| 位数: | 14 |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 4 |

| 电压电源: | 双 ± |

| 功率耗散(最大): | 310mW |

| 工作温度: | -40°C ~ 80°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm)裸露焊盘 |

| 供应商设备封装: | 24-TSSOP 裸露焊盘 |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | 4 电压,单极;4 电压,双极 |

| 采样率(每秒): | 100k |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD5724R/AD5734R/AD5754R

Rev. E | Page 29 of 32

POWER CONTROL REGISTER

The power control register is addressed by setting the three REG bits to 010. This register allows the user to control and determine the

power and thermal status of the AD5724R/AD5734R/AD5754R. The power control register options are shown in Table 27 and Table 28.

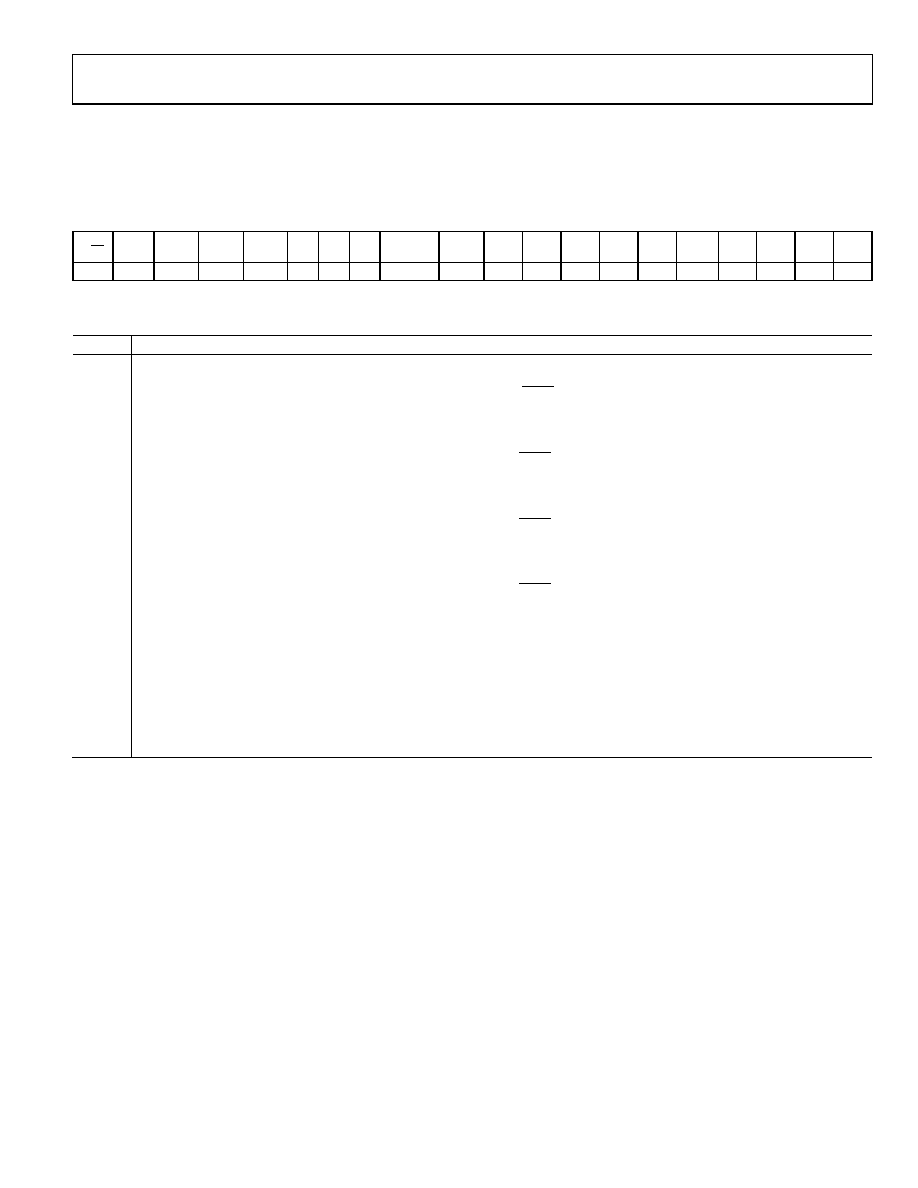

Table 27. Programming the Power Control Register

MSB

LSB

R/W

Zero

REG2

REG1

REG0

A2

A1

A0

DB15 to

DB11

DB10

DB9

DB8

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

0

1

0

X

OCD

OCC

OCB

OCA

0

TSD

PUREF

PUD

PUC

PUB

PUA

Table 28. Power Control Register Functions

Option

Description

PUA

DAC A power-up. When set, this bit places DAC A in normal operating mode. When cleared, this bit places DAC A in power-down

mode (default). After setting this bit to power DAC A, a power-up time of 10 μs is required. During this power-up time the DAC

register should not be loaded to the DAC output (see the Load DAC (LDAC) section). If the clamp enable bit of the control register

is cleared, DAC A powers down automatically on detection of an overcurrent, and PUA is cleared to reflect this.

PUB

DAC B power-up. When set, this bit places DAC B in normal operating mode. When cleared, this bit places DAC B in power-down

mode (default). After setting this bit to power DAC B, a power-up time of 10 μs is required. During this power-up time the DAC

register should not be loaded to the DAC output (see the Load DAC(LDAC) section). If the clamp enable bit of the control register

is cleared, DAC B powers down automatically on detection of an overcurrent, and PUB is cleared to reflect this.

PUC

DAC C power-up. When set, this bit places DAC C in normal operating mode. When cleared, this bit places DAC C in power-down

mode (default). After setting this bit to power DAC C, a power-up time of 10 μs is required. During this power-up time the DAC

register should not be loaded to the DAC output (see the Load DAC(LDAC) section). If the clamp enable bit of the control register

is cleared, DAC C powers down automatically on detection of an overcurrent, and PUC is cleared to reflect this.

PUD

DAC D power-up. When set, this bit places DAC D in normal operating mode. When cleared, this bit places DAC D in power-down

mode (default). After setting this bit to power DAC D, a power-up time of 10 μs is required. During this power-up time the DAC

register should not be loaded to the DAC output (see the Load DAC(LDAC) section). If the clamp enable bit of the control register

is cleared, DAC D powers down automatically on detection of an overcurrent, and PUD is cleared to reflect this.

PUREF

Reference power-up. When set, this bit places the internal reference in normal operating mode. When cleared, this bit places the

internal reference in power-down mode (default).

TSD

Thermal shutdown alert. Read-only bit. In the event of an overtemperature situation, the four DACs are powered down and this

bit is set.

OCA

DAC A overcurrent alert. Read-only bit. In the event of an overcurrent situation on DAC A, this bit is set.

OCB

DAC B overcurrent alert. Read-only bit. In the event of an overcurrent situation on DAC B, this bit is set.

OCC

DAC C overcurrent alert. Read-only bit. In the event of an overcurrent situation on DAC C, this bit is set.

OCD

DAC D overcurrent alert. Read-only bit. In the event of an overcurrent situation on DAC D, this bit is set.

相关PDF资料 |

PDF描述 |

|---|---|

| AD8138ARM-REEL7 | IC AMP DIFF LDIST LP 95MA 8MSOP |

| AD8138AR-REEL7 | IC AMP DIFF LDIST LP 95MA 8SOIC |

| LTC2610IUFD#TRPBF | IC DAC OCTAL R-R 14BIT 20-QFN |

| AD8310ARMZ-REEL7 | IC AMP LOGARITHMIC 8MSOP |

| VE-24P-IV-F1 | CONVERTER MOD DC/DC 13.8V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5735 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Channel, 16-Bit, Serial Input, 4-20mA & Voltage Output DAC, Dynamic Power Control |

| AD5735_12 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad-Channel, 12-Bit, Serial Input, 4 mA to 20 mA |

| AD5735ACPZ | 功能描述:IC DAC QUAD VOLT CUR 64-LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:1 系列:- 设置时间:4.5µs 位数:12 数据接口:串行,SPI? 转换器数目:1 电压电源:单电源 功率耗散(最大):- 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOICN 包装:剪切带 (CT) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):* 其它名称:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

| AD5735ACPZ-REEL7 | 功能描述:IC DAC QUAD VOLT CUR 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD5737 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Channel, 16-Bit, Serial Input, 4-20mA Output DAC, Dynamic Power Control, HART Connectivity |

发布紧急采购,3分钟左右您将得到回复。