参数资料

| 型号: | AD5781BRUZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/28页 |

| 文件大小: | 0K |

| 描述: | IC DAC 18BIT SRL 20TSSOP |

| 产品变化通告: | AD57x1 Feature Change 27/Jul/2011 |

| 设计资源: | 18-Bit Accurate, low noise, precision bipolar DC voltage source (CN0177) |

| 标准包装: | 1,000 |

| 设置时间: | 1µs |

| 位数: | 18 |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 带卷 (TR) |

| 输出数目和类型: | * |

| 采样率(每秒): | 1M |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Data Sheet

AD5781

Rev. D | Page 19 of 28

THEORY OF OPERATION

The AD5781 is a high accuracy, fast settling, single, 18-bit,

serial input, voltage output DAC. It operates from a VDD supply

voltage of 7.5 V to 16.5 V and a VSS supply of 16.5 V to 2.5 V.

Data is written to the AD5781 in a 24-bit word format via a 3-wire

serial interface. The AD5781 incorporates a power-on reset

circuit that ensures the DAC output powers up to 0 V with the

VOUT pin clamped to AGND through a ~6 kΩ internal resistor.

DAC ARCHITECTURE

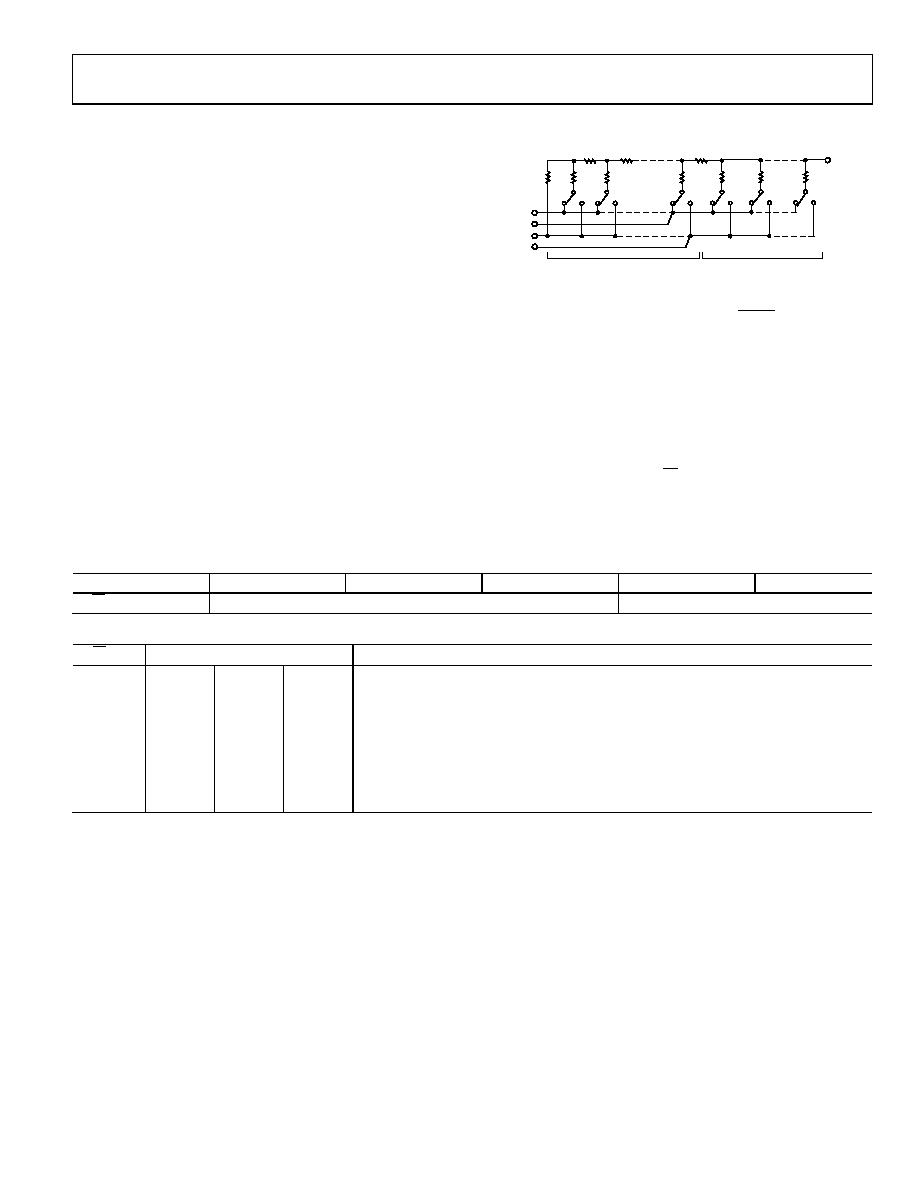

The architecture of the AD5781 consists of two matched DAC

sections. A simplified circuit diagram is shown in Figure 49.

The six MSBs of the 18-bit data-word are decoded to drive 63

switches, E0 to E62. Each of these switches connects one of 63

matched resistors to either the VREFP or VREFN voltage. The

remaining 12 bits of the data-word drive the S0 to S11 switches

of a 12-bit voltage mode R-R ladder network.

2R

S0

2R

S1

2R

S11

2R

E62

2R

E61

2R

E0

12-BIT R-R LADDER

.....................

..........

RR

R

2R

VREFPF

VREFPS

VREFNF

VREFNS

VOUT

SIX MSBs DECODED INTO

63 EQUAL SEGMENTS

090

92-

053

Figure 49. DAC Ladder Structure Serial Interface

The AD5781 has a 3-wire serial interface (SYNC, SCLK, and

SDIN) that is compatible with SPI, QSPI, and MICROWIRE

interface standards, as well as most DSPs (see Figure 2 for a

timing diagram).

Input Shift Register

The input shift register is 24 bits wide. Data is loaded into the

device MSB first as a 24-bit word under the control of a serial

clock input, SCLK, which can operate at up to 35 MHz. The

input register consists of a R/W bit, three address bits, and

twenty data bits as shown in Table 7. The timing diagram for

this operation is shown in Figure 2.

Table 7. Input Shift Register Format

MSB

LSB

DB23

DB22

DB21

DB20

DB19

DB0

R/W

Register address

Register data

Table 8. Decoding the Input Shift Register

R/W

Register Address

Description

0

No operation (NOP). Used in readback operations.

0

1

Write to the DAC register.

0

1

0

Write to the control register.

0

1

Write to the clearcode register.

0

1

0

Write to the software control register.

1

0

1

Read from the DAC register.

1

0

1

0

Read from the control register.

1

0

1

Read from the clearcode register.

1 X is don’t care.

相关PDF资料 |

PDF描述 |

|---|---|

| AD5790BCPZ | IC DAC VOLT OUT 20BIT 24LFCSP |

| AD5791BRUZ | IC DAC 20BIT SRL 20TSSOP |

| AD5821ABCBZ-REEL | IC DAC 10BIT CURRENTSINK 9WLCSP |

| AD6600ASTZ | IC ADC DUAL W/RSSI 44-LQFP |

| AD6644ASTZ-65 | IC ADC 14BIT 65MSPS CMOS 52-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5781SRU-EP | 功能描述:数模转换器- DAC 18-Bit VOut +/-0.5 LSB INL RoHS:否 制造商:Analog Devices 转换器数量:4 DAC 输出端数量:4 转换速率: 分辨率:12 bit 接口类型:Serial (I2C) 稳定时间: 最大工作温度:+ 105 C 安装风格: 封装 / 箱体:TSSOP 封装:Reel |

| AD578221 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| AD578JD | 制造商:AD 制造商全称:Analog Devices 功能描述:VERY FAST, COMPLETE 10- OR 12-BIT A/D CONVERTERS |

| AD578JN | 制造商:AD 制造商全称:Analog Devices 功能描述:VERY FAST, COMPLETE 10- OR 12-BIT A/D CONVERTERS |

| AD578K | 制造商:AD 制造商全称:Analog Devices 功能描述:VERY FAST, COMPLETE 10- OR 12-BIT A/D CONVERTERS |

发布紧急采购,3分钟左右您将得到回复。