参数资料

| 型号: | AD6620ASZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 25/44页 |

| 文件大小: | 0K |

| 描述: | IC DGTL RCVR DUAL 67MSPS 80-PQFP |

| 标准包装: | 1 |

| 接口: | 并行/串行 |

| 电源电压: | 3 V ~ 3.6 V |

| 封装/外壳: | 80-BQFP |

| 供应商设备封装: | 80-PQFP(14x14) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

| 产品目录页面: | 551 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD6620

–31–

REV. A

ACCESS PROTOCOLS

The AD6620 external accesses may be performed through either

the Microprocessor Port or the Serial Port. The Microport and

the serial port both use a three-bit address and eight-bit data to

access these registers. The three-bit address provides access to

seven register locations (External Interface Registers). These

register locations are used to access the internal address space of

the AD6620 shown in the Control Register section. The seven

registers are the LAR (Low Address Register), the AMR (Address

Mode Register), and the five data registers (DR4–DR0).

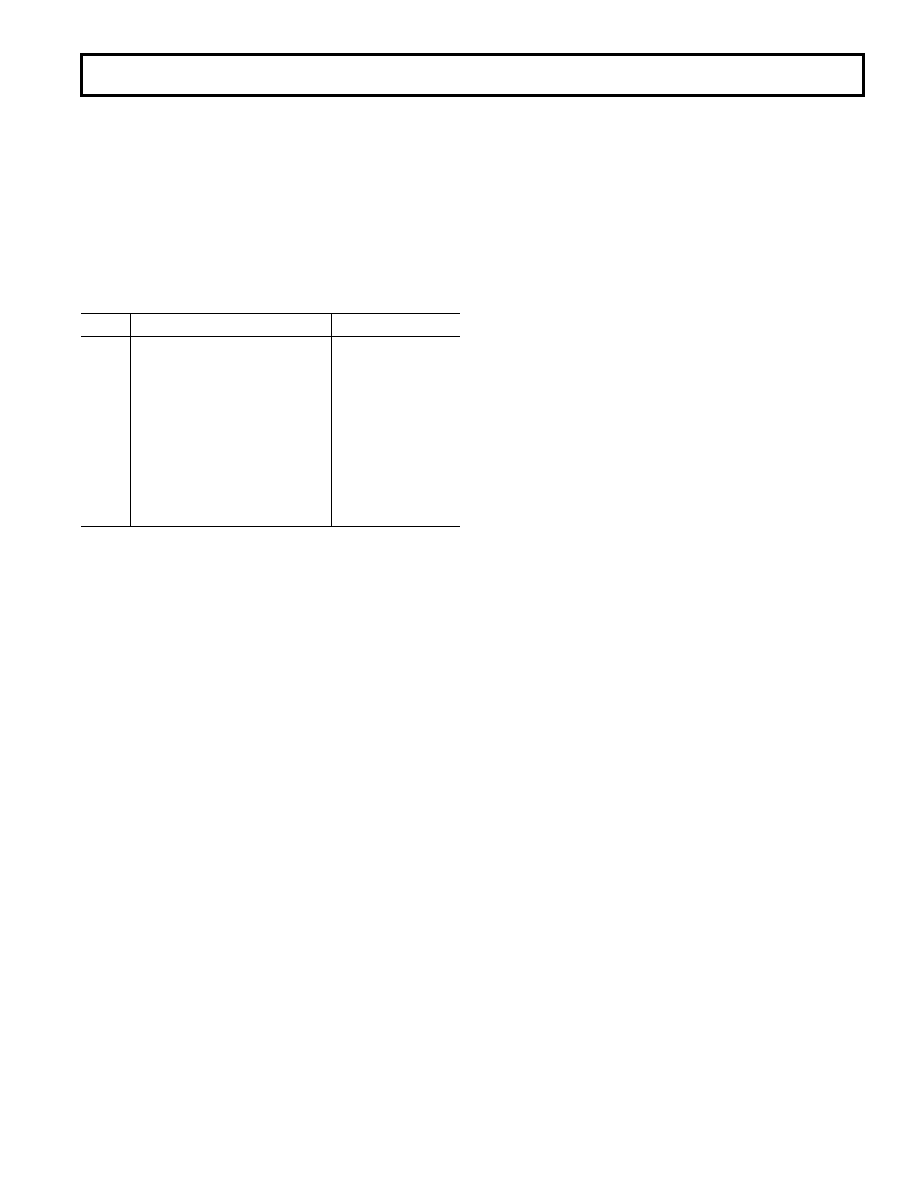

Table XI. External Interface Registers

A[2:0]

Name

Comment

000

Data Register 0 (DR0)

D[7:0]

001

Data Register 1 (DR1)

D[15:8]

010

Data Register 2 (DR2)

D[23:16]

011

Data Register 3 (DR3)

D[31:24]

100

Data Register 4 (DR4)

D[35:32]

101

Reserved

110

Low Address Register (LAR)

A[7:0]

111

Address Mode Register (AMR)

1-0: A[9:8]

5-2: Reserved

6: Read Increment

7: Write Increment

The internal address space is accessed using a 10-bit internal

address. Many of these address locations are more than a byte

wide and require multiple accesses to the seven External Inter-

face Registers, which are each only 8 bits wide (only 4 bits of

DR4 are used). Accesses to these registers are accomplished

using the 3-bit address and 8-bit data lines the manner described

below. The source of these values depends on the control port

method used.

All internal accesses are accomplished by first writing the inter-

nal address of the register or memory location to be accessed.

The lower eight address bits are written to the LAR register

and the upper two address bits to the LSBs of the AMR. This

defines the internal address of the location to be accessed as

shown in the memory map shown in the Control Registers and

On-Chip RAM section.

Internal Write Access

Up to 36 bits of data (as needed) can be written by the process

described below. Any high order bytes that are needed are writ-

ten to the corresponding data registers defined in the external

3-bit address space. The least significant byte is then written to

DR0 at address (000). When a write to DR0 is detected, the

internal microprocessor port state machine then moves the data

in DR4–DR0 to the internal address pointed to by the address

in the LAR and AMR.

Write Pseudocode

void write_micro(ext_address, int data);

main();

{

/

* This code shows the programming of the NCO frequency

register using the write_micro function as defined above. The

variable address is the External Address A[2:0] and data is the

value to be placed in the external interface register. The NCO

register is located at Internal Address = 0x303

*/

// holding registers for NCO byte wide access data

int d3, d2, d1, d0;

// NCO frequency word (32-bits wide)

NCO_FREQ = 0xCBEFEFFF;

// write AMR

write_micro(7, 0x03);

// write LAR

write_micro(6, 0x03);

// DR4 is not needed because NCO_FREQ is only 32-bits, not

36

// write DR3 with high byte of 32 bit word (D[31:24]

d3 = (NCO_FREQ & 0xFF000000) >> 24;

write_micro(3, d3);

// write DR2 with high byte of 32 bit word (D[23:16]

d2 = (NCO_FREQ & 0xFF0000) >> 16;

write_micro(2, d2);

// write DR1 with D[15:8]

d1 = (NCO_FREQ & 0xFF00) >> 8;

write_micro(1, d1);

// write DR0 with D[7:0]

// Writing to DR0 causes all data to be transferred to the

internal address.

//Therefore, DR1, DR2 and DR3 should already be written

d0 = NCO_FREQ & 0xFF;

write_micro(0, d0);

} // end of main

Internal Read Access

A read is performed by first writing the LAR and AMR as with a

write. The data registers (DR4–DR0) are then read in the reverse

order that they were written. First, the least significant byte of

the data (D[7:0]) is read from DR0. On this transaction the

high bytes of the data are moved from the internal address

pointed to by the LAR and AMR into the remaining data regis-

ters (DR4–DR1). This data can then be read from the data

registers using the appropriate 3-bit addresses. The number of

data registers used depends solely on the amount of data to be

read or written. Any unused bit in a data register should be

masked out for a read.

相关PDF资料 |

PDF描述 |

|---|---|

| AD6623ASZ | IC TSP 4CHAN 104MSPS 128MQFP |

| AD6641BCPZRL7-500 | IC IF RCVR 11BIT 200MSPS 56LFCSP |

| AD664BJ | IC DAC 12BIT QUAD MONO 44-JLCC |

| AD667BD | IC DAC 12BIT W/BUFF LTCH 28-CDIP |

| AD669BN | IC DAC 16BIT MONO VREF 28-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6620ASZ-REEL | 功能描述:IC DGTL RCVR DUAL 67MSPS 80-PQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6620PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

发布紧急采购,3分钟左右您将得到回复。