参数资料

| 型号: | AD6620ASZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/44页 |

| 文件大小: | 0K |

| 描述: | IC DGTL RCVR DUAL 67MSPS 80-PQFP |

| 标准包装: | 1 |

| 接口: | 并行/串行 |

| 电源电压: | 3 V ~ 3.6 V |

| 封装/外壳: | 80-BQFP |

| 供应商设备封装: | 80-PQFP(14x14) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

| 产品目录页面: | 551 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD6620

–38–

REV. A

APPLICATIONS

EVALUATION BOARD

An evaluation board is available for the AD6620. This evalua-

tion board comes complete with an AD6620 and interfaces to a

PC through the printer port. The evaluation board comes com-

plete with software to drive the evaluation board and to design

optimized filters for use with the AD6620. The evaluation board

includes a high speed data interface that mates directly with

evaluation boards for high performance converters such as the

AD6600 and AD6640, allowing digital receivers to be bread-

boarded with only an external RF/IF converter and an interface

to the DSP.

The control software allows access to all of the internal registers

to provide complete programming of the device in a lab setting.

The software can process high speed data as well as digitally

filtered data from the AD6620 allowing analysis of both pre and

post filter channel characteristics. The controlling software can

also be used to verify the filter performance by sweeping the NCO,

greatly simplifying verification of any given filter design.

AD6620

HI SPEED

DATA

HEADER

LATCH

FIFO

PC PRINTER PORT

LATCH

TRANSCEIVER

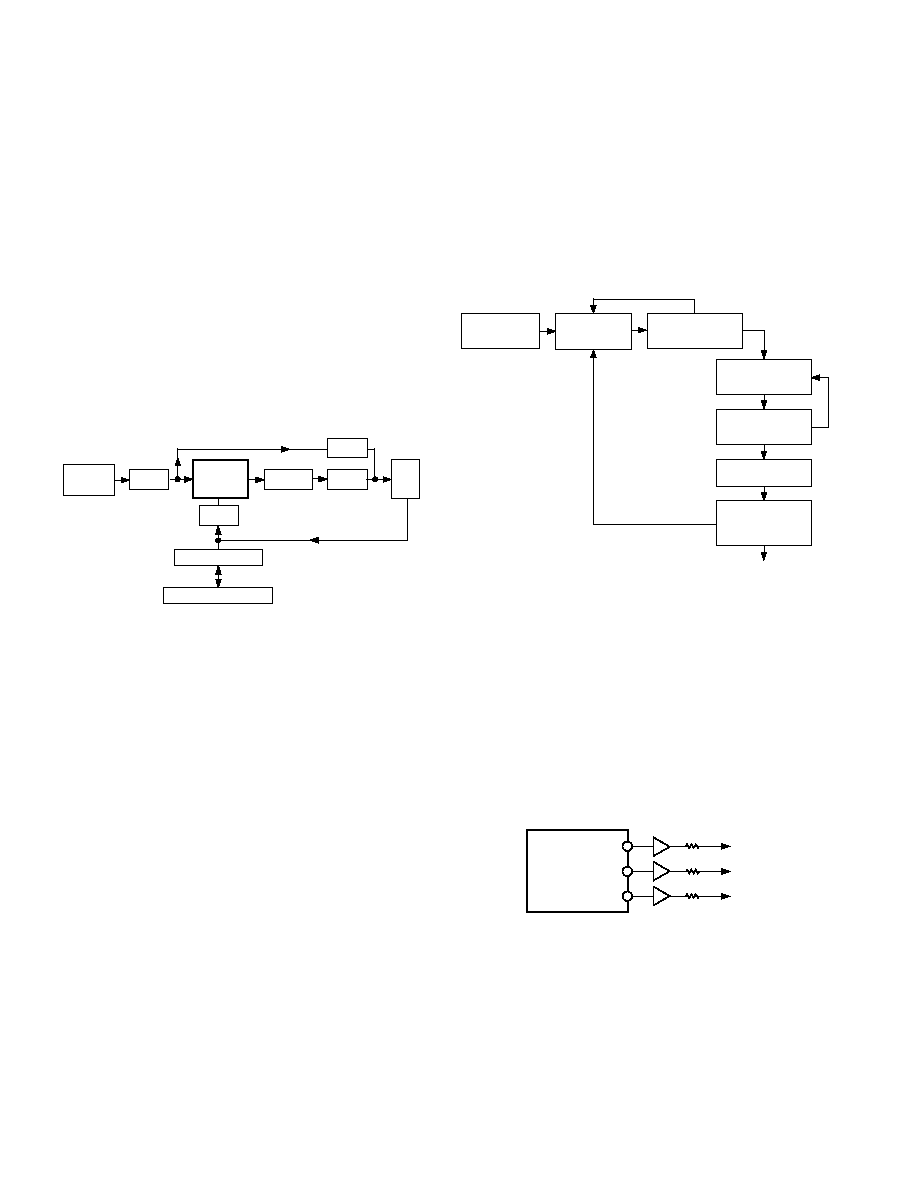

Figure 47. Evaluation Board Block Diagram

As shown in the block diagram below, the high speed data into

the evaluation board is sent to both the AD6620 and the by-pass

latches. On the output of the AD6620, data is available in either

serial or parallel mode. In serial mode, data may be sent directly

to a DSP for system bread-boarding. In parallel mode, the data

may be sent to the on-board FIFO for spectral analysis by the

included software. For additional information, refer to the evalua-

tion board manual.

FILTER DESIGN

The AD6620 implements a pair of cascaded CIC filters with a

sum of products FIR filter. The frequency characteristics of the

CIC filters have already been documented. Additional reading

on this class of filters can be found in “An Economical Class of

Digital Filters for Decimation and Interpolation,” by Eugene B.

Hogenauer, IEEE Transactions on Acoustics, Speech, and Signal

Processing, Volume ASSP-29, Number 2, April 1981.

The characteristics of the FIR filter are fully programmable.

The coefficients of this filter may be generated in any number

of ways, using standard procedures such as Parks-McClellan.

Available software from Analog Devices that assists in the design

of filters for this product. This software allows comparison

between different distributions of decimation. The software

works independently of the evaluation board, but easily allows

transfer of design data directly to the evaluation board for

immediate verification of the designed filter.

The normal procedure for designing a filter for the chip is as

shown in the flow chart. First, the desired characteristics must

be determined based on the receive channel requirements. The

decimation rates for the CIC filters must then be selected such

that their performance is near that of the desired channel require-

ments. Finally, an algorithm such as the Parks-McClellan or

Remez exchange is used to compute the final spectral require-

ments, including droop correction for passband loss of the CIC

filters. If the designed filter meets the requirements, then the

filter is acceptable. If not, another combination of CIC filter

decimation must be examined. Tables III and IV greatly simplify

distribution and selection of CIC requirements. The filter

software available from Analog Devices helps to automate

this procedure.

SELECT FILTER

REJECTION

REQUIREMENTS

DOES CIC2 FILTER

PROTECT ENOUGH

BANDWIDTH?

SELECT

DECIMATION

RATE FOR CIC5

DESIGN RCF WITH

REMEZ EXCHANGE

NO

YES

SELECT

DECIMATION

RATE FOR CIC2

DOES CIC5 FILTER

PROTECT ENOUGH

BANDWIDTH?

DOES COMPOSITE

FILTER PROVIDE

THE DESIRED

RESULTS?

YES

NO

YES

NO

Figure 48. Diagram of Filter Design Software

SERIAL BUFFERING

The AD6620 serial outputs are designed to operate at very high

speed. As such, care must be taken when driving the serial output

lines. These high speed lines must be treated as transmission

lines. Critical lines include the SCLK, SDFS, SDFE, SDI and

SDO. It is recommended that these lines be series source termi-

nated with the characteristic impedance of the driven line. If the

lines are longer than a few inches, digital line buffers should be

used as shown below. Buffering in this manner will prevent

reflections on the serial lines from disrupting operation of the

AD6620. A good reference on transmission lines is found in the

“MECL System Design Handbook” by Motorola Inc., Stock

code HB205R1/D.

AD6620

SCLK

SDO

SDFS

SCLK

SDO

SDFS

Figure 49. Serial Line Buffering and Series Source

Termination

DSP/SHARC INTERFACING

With little effort, the AD6620 will interface to nearly all indus-

try standard DSPs, as shown in the figure below. The figures

below show operation in TDM applications as well as in serial

slave mode.

In TDM mode the first AD6620 is configured to be the master.

This chip is the first to access the serial data bus. When the

master has data available in its output shifters, it generates an

SDFS telling the DSP that serial data will follow. At this point,

相关PDF资料 |

PDF描述 |

|---|---|

| AD6623ASZ | IC TSP 4CHAN 104MSPS 128MQFP |

| AD6641BCPZRL7-500 | IC IF RCVR 11BIT 200MSPS 56LFCSP |

| AD664BJ | IC DAC 12BIT QUAD MONO 44-JLCC |

| AD667BD | IC DAC 12BIT W/BUFF LTCH 28-CDIP |

| AD669BN | IC DAC 16BIT MONO VREF 28-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6620ASZ-REEL | 功能描述:IC DGTL RCVR DUAL 67MSPS 80-PQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

| AD6620PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S | 制造商:AD 制造商全称:Analog Devices 功能描述:65 MSPS Digital Receive Signal Processor |

| AD6620S/PCB | 制造商:Analog Devices 功能描述:DUAL CHANNEL DECIMATING RECEIV 制造商:Analog Devices 功能描述:SGNL PROCESSOR 169CSPBGA - Bulk |

| AD6622 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 75 MSPS Digital Transmit Signal Processor TSP |

发布紧急采购,3分钟左右您将得到回复。