- 您现在的位置:买卖IC网 > PDF目录10278 > AD7262BSTZ-RL7 (Analog Devices Inc)IC ADC 12BIT W/PGA&COM 48-LQFP PDF资料下载

参数资料

| 型号: | AD7262BSTZ-RL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 21/33页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT W/PGA&COM 48-LQFP |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 1M |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 120mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 标准包装 |

| 输入数目和类型: | 2 个差分,单极 |

| 产品目录页面: | 777 (CN2011-ZH PDF) |

| 其它名称: | AD7262BSTZ-RL7DKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

AD7262

Rev. 0 | Page 27 of 32

CALIBRATION

The AD7262/AD7262-5 registers store the offset value that can

be accessed easily by the user (see the Reading from a Register

section). When the device is calibrating, the differential analog

inputs for each respective ADC are shorted together internally

and a conversion is performed. A digital code representing the

offset is stored internally in the offset registers, and subsequent

conversion results have this measured offset removed.

INTERNAL OFFSET CALIBRATION

The AD7262/AD7262-5 allow the user to calibrate the device

offset using the CAL pin. This is achieved by setting the CAL

pin to a high logic level, which initiates a calibration on the next

CS falling edge. The calibration requires one full conversion

cycle, which contains a CS falling edge followed by 19 SCLKs to

complete. The CAL pin can remain high for more than one

conversion if desired, and the AD7262/AD7262-5 continue to

calibrate.

When the AD7262/AD7262-5 are calibrated, the calibration

results stored in the internal device registers are only relevant

for the particular PGA gain selected at the time of calibration. If

the PGA gain is changed, the AD7262/AD7262-5 must be

recalibrated. If the device is not recalibrated when the PGA gain

is changed, the offset for the previous gain setting continues to

be removed from the digital output code, which may lead to

inaccuracies.

The CAL pin should only be driven high when the CS pin is high

or after 19 SCLK cycles have elapsed when CS is low (that is,

between conversions). The CAL pin must be driven high t12 ns

before CS goes low. If the CS pin goes low before the t12 has

elapsed, the calibration result is inaccurate for the current

conversion, but, provided that the CAL pin remains high, the

subsequent calibration conversion is correct. If the CAL pin is

set to a logic high state during a conversion, that conversion result

is corrupted.

The offset range, which can be calibrated for, is ±128 least

significant bits at a gain of 1. The maximum offset voltage,

which can be calibrated for, is reduced as the gain of the PGA

is increased.

Provided that the CAL pin has been held high for a minimum

of one conversion, and once t12 and t11 have been adhered to, the

calibration is complete after the 19th SCLK cycle, and the CAL

pin can be driven to a logic low state. The next CS falling edge

after the CAL pin has been driven to a low logic state initiates

a conversion of the differential analog input signal for both

ADC A and ADC B.

Table 12 details the maximum offset voltage, which can be

removed by the AD7262/AD7262-5 without compromising the

available digital output code range. The least significant bit size is

AVCC/2BITs, which is 5/4096 or 1.22 mV for the

AD7262/

AD7262-5. The maximum removable offset voltage is

given by

Gain

mV

22

.

1

LSB

128

×

±

Table 12. Offset Range

Alternatively, one can use the control register to initiate an

offset calibration. This is done by setting the CAL bit in the

control register to 1. The calibration is then initiated on the next

CS falling edge, but the current conversion is corrupted. The

ADCs on the AD7262/AD7262-5 must remain fully powered

up to complete the internal calibration.

Gain

Maximum Removable Offset Voltage

1

±156.16 mV

2

±78.08 mV

3

±52.053 mV

32

±4.88 mV1

1 This is the maximum removable offset for PGA gain ≥ 32.

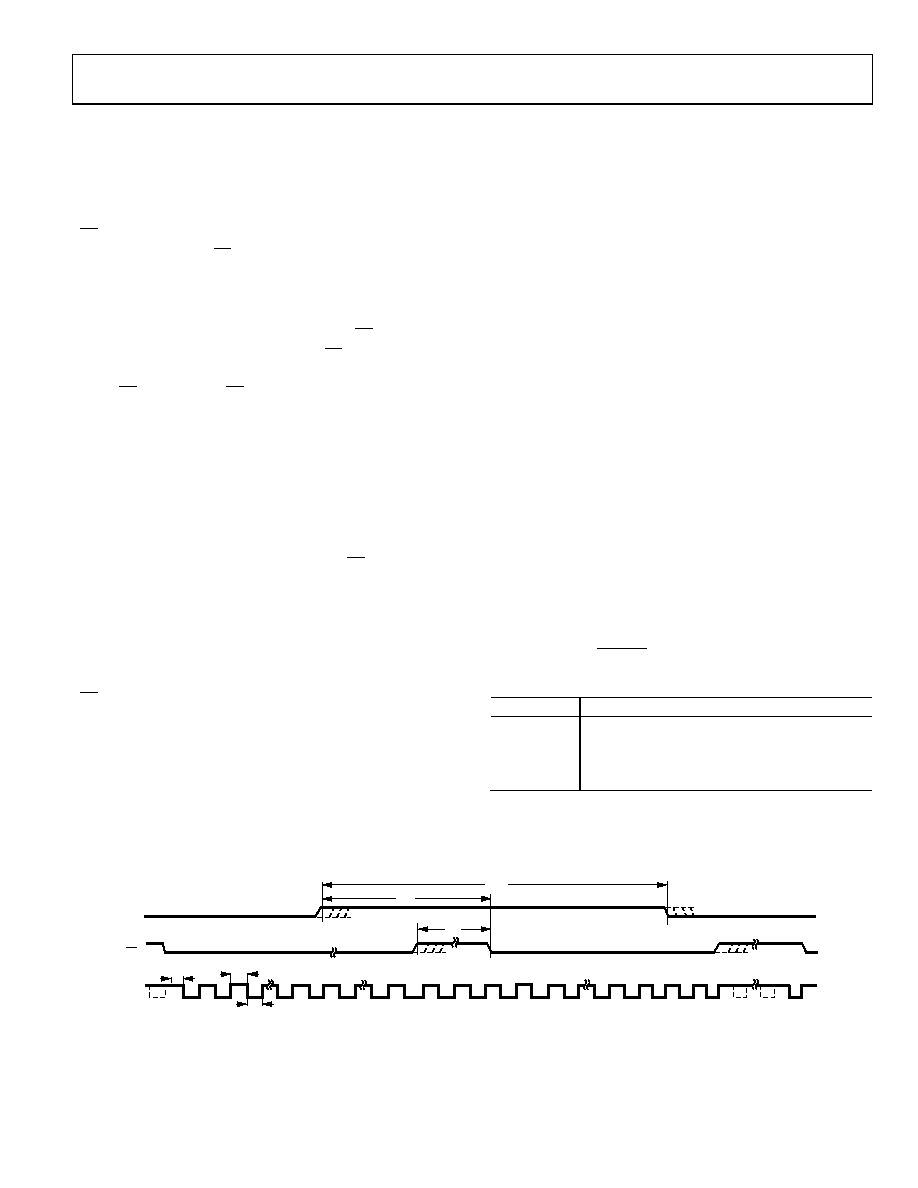

CS

SCLK

CAL

20

12

3

21

19

t2

t6

t8

t7

t12

t11

31

30

21

20

19

3

2

1

07

60

6-

03

6

Figure 36. Calibration Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/20KC98AA | CONN HSG RCPT 10POS WALL MT PINS |

| V24B3V3H150BL2 | CONVERTER MOD DC/DC 3.3V 150W |

| MS27472T18C32P | CONN RCPT 32POS WALL MT W/PINS |

| VE-JNH-MX-S | CONVERTER MOD DC/DC 52V 75W |

| MS27473E10F13SD | CONN PLUG 13POS STRAIGHT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7264 | 制造商:AD 制造商全称:Analog Devices 功能描述:1 MSPS, 14-Bit, Simultaneous Sampling SAR ADC with PGA and Four Comparators |

| AD7264BCPZ | 功能描述:IC ADC 14BIT 2CH 1MSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7264BCPZ-5 | 功能描述:IC ADC 14BIT 2CH 500KSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7264BCPZ-5-RL7 | 功能描述:IC ADC 14BIT 2CH 500KSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7264BCPZ-RL7 | 功能描述:IC ADC 14BIT 2CH 1MSPS 48LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

发布紧急采购,3分钟左右您将得到回复。