- 您现在的位置:买卖IC网 > PDF目录1980 > AD7265BSUZ-REEL7 (Analog Devices Inc)IC ADC 12BIT 3CHAN 1MSPS 32TQFP PDF资料下载

参数资料

| 型号: | AD7265BSUZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/29页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT 3CHAN 1MSPS 32TQFP |

| 设计资源: | AD7265 in Differential and Single-Ended Configurations Using AD8022 (CN0048) |

| 标准包装: | 500 |

| 位数: | 12 |

| 采样率(每秒): | 1M |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 21mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 12 个单端,单极;6 个差分,单极;6 个伪差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

AD7265

Rev. A | Page 20 of 28

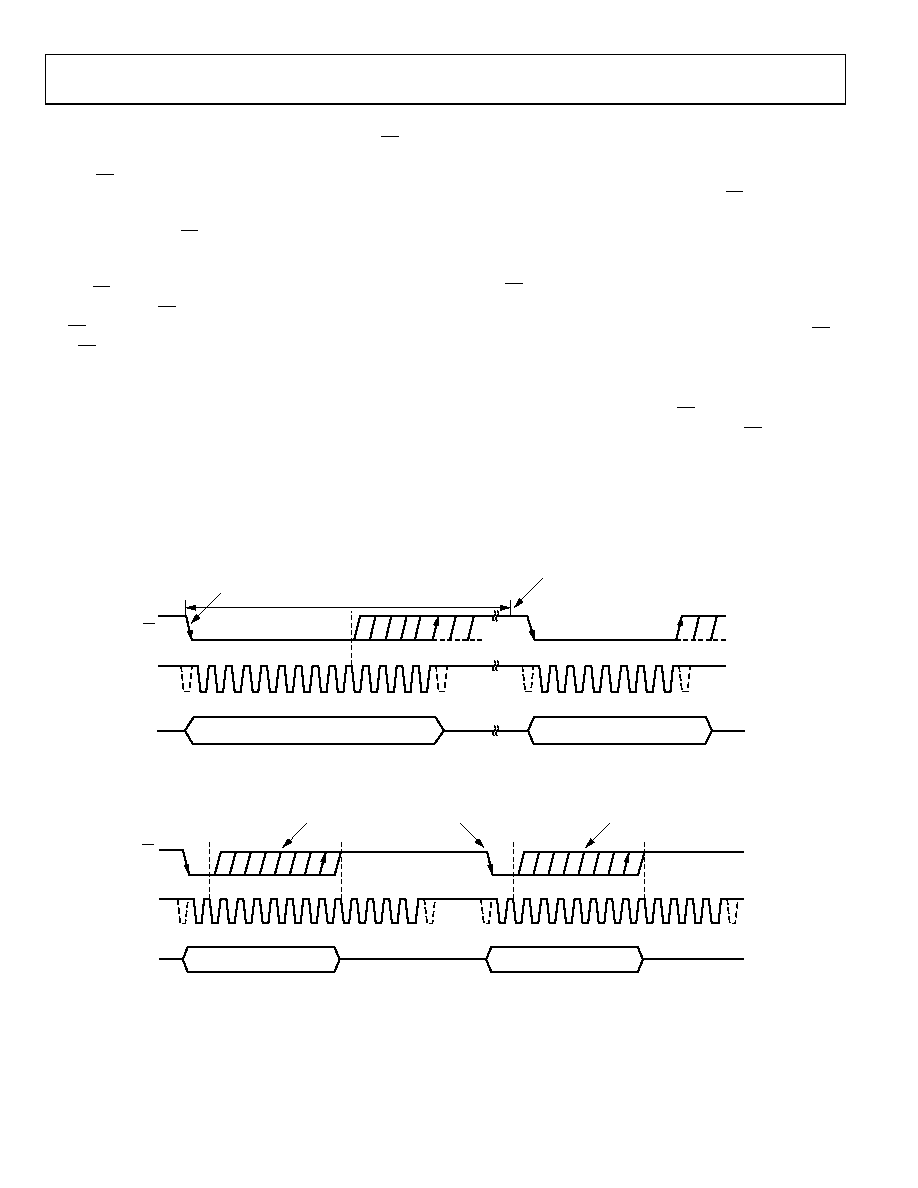

To exit this mode of operation and power up the AD7265 again,

a dummy conversion is performed. On the falling edge of CS,

the device begins to power up and continues to power up as

long as CS is held low until after the falling edge of the 10th

SCLK. The device is fully powered up after approximately 1 μs

has elapsed, and valid data results from the next conversion, as

shown in Figure 36. If CS is brought high before the second

falling edge of SCLK, the AD7265 again goes into partial

power-down. This avoids accidental power-up due to glitches

on the CS line. Although the device may begin to power up on

the falling edge of CS, it powers down again on the rising edge

of CS. If the AD7265 is already in partial power-down mode

and CS is brought high between the second and 10th falling

edges of SCLK, the device enters full power-down mode.

FULL POWER-DOWN MODE

This mode is intended for use in applications where throughput

rates slower than those in the partial power-down mode are

required, as power-up from a full power-down takes

substantially longer than that from partial power-down. This

mode is more suited to applications where a series of

conversions performed at a relatively high throughput rate are

followed by a long period of inactivity and thus power-down.

When the AD7265 is in full power-down, all analog circuitry is

powered down. Full power-down is entered in a similar way as

partial power-down, except the timing sequence shown in

Figure 35 must be executed twice. The conversion process must

be interrupted in a similar fashion by bringing CS high anywhere

after the second falling edge of SCLK and before the 10th falling

edge of SCLK. The device enters partial power-down at this

point. To reach full power-down, the next conversion cycle

must be interrupted in the same way, as shown in Figure 37.

Once CS is brought high in this window of SCLKs, the part

completely powers down.

CS

Note that it is not necessary to complete the 14 SCLKs once

is brought high to enter a power-down mode.

To exit full power-down and power up the AD7265, a dummy

conversion is performed, as when powering up from partial

power-down. On the falling edge of CS, the device begins to

power up and continues to power up, as long as CS is held low

until after the falling edge of the 10th SCLK. The required

power-up time must elapse before a conversion can be initiated,

as shown in Figure 38. See the Power-Up Times section for the

power-up times associated with the AD7265.

SCLK

CS

DOUTA

DOUTB

INVALID DATA

VALID DATA

110

14

1

THE PART BEGINS

TO POWER UP.

THE PART IS FULLY

POWERED UP; SEE

POWER-UP TIMES

SECTION.

tPOWER-UP1

04674-031

Figure 36. Exiting Partial Power-Down Mode

THREE-STATE

110

14

2

SCLK

CS

DOUTA

DOUTB

THREE-STATE

110

2

INVALID DATA

THE PART BEGINS

TO POWER UP.

THE PART ENTERS

PARTIAL POWER DOWN.

THE PART ENTERS

FULL POWER DOWN.

04674-032

14

Figure 37. Entering Full Power-Down Mode

相关PDF资料 |

PDF描述 |

|---|---|

| AD7266BSUZ | IC ADC 12BIT 3CH 2MSPS 32-TQFP |

| AD7274BRM | IC ADC 12BIT 3MSPS HS LP 8MSOP |

| AD7276BRM | IC ADC 12BIT 3MSPS HS LP 8MSOP |

| AD7291BCPZ-RL7 | IC ADC I2C/SRL 22.22K 20LFCSP |

| AD7298-1BCPZ-RL | IC ADC 10BIT SPI/SRL 8CH 20LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7266 | 制造商:Analog Devices 功能描述:- Bulk |

| AD7266ACP | 制造商:Analog Devices 功能描述:ADC DUAL SAR 2MSPS 12-BIT SERL 32LFCSP - Bulk |

| AD7266ASU | 制造商:Analog Devices 功能描述:ADC DUAL SAR 2MSPS 12-BIT SERL 32TQFP - Bulk |

| AD7266BCP | 制造商:Analog Devices 功能描述:ADC Dual SAR 2Msps 12-bit Serial 32-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:DUAL, 2 MSPS, 3-CH SIMULTANEOUS SAMPLING ADC - Bulk |

| AD7266BCP-U1 | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。