- 您现在的位置:买卖IC网 > PDF目录10672 > AD7328BRUZ (Analog Devices Inc)IC ADC 12BIT+ SAR 8CHAN 20TSSOP PDF资料下载

参数资料

| 型号: | AD7328BRUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 27/37页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT+ SAR 8CHAN 20TSSOP |

| 设计资源: | Using AD7328 in Appls with Single-Ended Industrial-Level Signals (CN0047) |

| 标准包装: | 75 |

| 系列: | iCMOS® |

| 位数: | 12 |

| 采样率(每秒): | 1M |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 30mW |

| 电压电源: | 双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

| 输入数目和类型: | 8 个单端,单极;8 个单端,双极;4 个差分,单极;4 个差分,双极 |

| 产品目录页面: | 777 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

AD7328

Data Sheet

Rev. C | Page 32 of 36

MICROPROCESSOR INTERFACING

The serial interface on the AD7328 allows the part to be directly

connected to a range of different microprocessors. This section

explains how to interface the AD7328 with some common

microcontroller and DSP serial interface protocols.

The ADSP-21xx family of DSPs interfaces directly to the AD7328

the same supply voltage as that of the ADSP-21xx. This allows

the ADC to operate at a higher supply voltage than its serial inter-

face. The SPORT0 on the ADSP-21xx should be configured as

shown in Table 14.

Table 14. SPORT0 Control Register Setup

Setting

Description

TFSW = RFSW = 1

Alternative framing

INVRFS = INVTFS = 1

Active low frame signal

DTYPE = 00

Right justify data

SLEN = 1111

16-bit data-word

ISCLK = 1

Internal serial clock

TFSR = RFSR = 1

Frame every word

IRFS = 0

Internal receive frame sync

ITFS = 1

Internal transmit frame sync

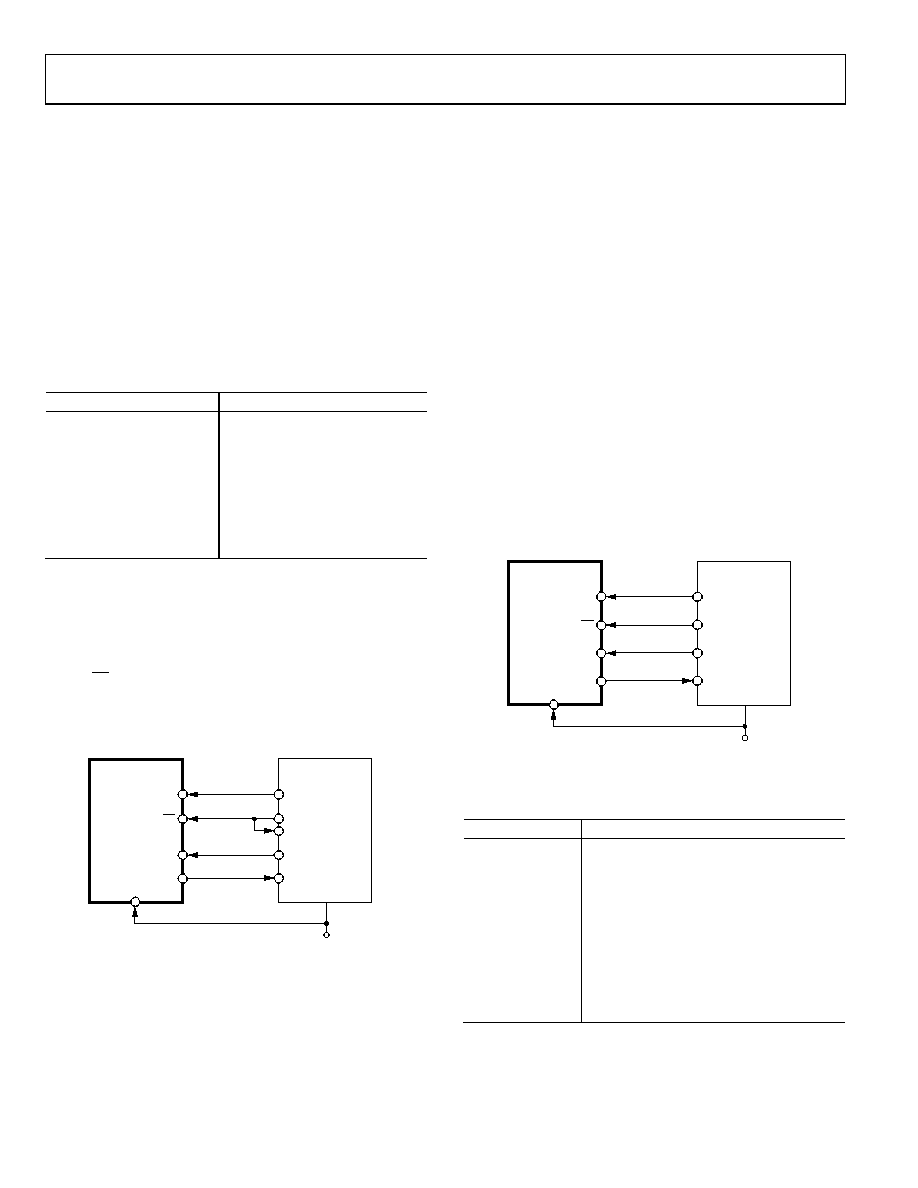

The connection diagram is shown in Figure 54. The ADSP-21xx

has TFS0 and RFS0 tied together. TFS0 is set as an output, and

RFS0 is set as an input. The DSP operates in alternative framing

mode, and the SPORT0 control register is set up as described in

Table 14. The frame synchronization signal generated on TFS is

tied to CS and, as with all signal processing applications, requires

equidistant sampling. However, as in this example, the timer

interrupt is used to control the sampling rate of the ADC, and

under certain conditions equidistant sampling cannot be achieved.

AD73281

ADSP-21xx1

SCLK

SCLK0

CS

TFS0

RFS0

DOUT

DIN

DT0

DR0

VDD

VDRIVE

1ADDITIONAL PINS OMITTED FOR CLARITY.

04852-

037

Figure 54. Interfacing the AD7328 to the ADSP-21xx

The timer registers are loaded with a value that provides an

interrupt at the required sampling interval. When an interrupt

is received, a value is transmitted with TFS/DT (ADC control

word). The TFS is used to control the RFS and, hence, the reading

of data.

The frequency of the serial clock is set in the SCLKDIV register.

When the instruction to transmit with TFS is given (AX0 = TX0),

the state of the serial clock is checked. The DSP waits until the

SCLK has gone high, low, and high again before starting the trans-

mission. If the timer and SCLK are chosen so that the instruction

to transmit occurs on or near the rising edge of SCLK, data can

be transmitted immediately or at the next clock edge.

For example, if the ADSP-21xx has a master clock frequency of

16 MHz and the SCLKDIV register is loaded with the value 3,

an SCLK of 2 MHz is obtained, and eight master clock periods

elapse for every one SCLK period. If the timer registers are loaded

with the value 803, 100.5 SCLKs occur between interrupts and,

subsequently, between transmit instructions. This situation leads

to nonequidistant sampling because the transmit instruction occurs

on an SCLK edge. If the number of SCLKs between interrupts is

an integer of N, equidistant sampling is implemented by the DSP.

The ADSP-BF53x family of DSPs interfaces directly to the

AD7328 without requiring glue logic, as shown in Figure 55.

The SPORT0 Receive Configuration 1 register should be set up

as outlined in Table 15.

AD73281

ADSP-BF53x1

VDD

VDRIVE

SCLK

RSCLK0

DIN

DT0

DOUT

DR0

CS

RFS0

1ADDITIONAL PINS OMITTED FOR CLARITY.

04852-

038

Figure 55. Interfacing the AD7328 to the ADSP-BF53x

Table 15. SPORT0 Receive Configuration 1 Register

Setting

Description

RCKFE = 1

Sample data with falling edge of RSCLK

LRFS = 1

Active low frame signal

RFSR = 1

Frame every word

IRFS = 1

Internal RFS used

RLSBIT = 0

Receive MSB first

RDTYPE = 00

Zero fill

IRCLK = 1

Internal receive clock

RSPEN = 1

Receive enable

SLEN = 1111

16-bit data-word

TFSR = RFSR = 1

Transmit and receive frame sync

相关PDF资料 |

PDF描述 |

|---|---|

| AD7476AYKSZ-500RL7 | IC ADC 12BIT 1MSPS SC70-6 |

| NCS2200SN2T1G | IC COMPARATOR 1V LOW PWR 5TSOP |

| DS90CR218AMTD/NOPB | IC RCVR 21BIT CHAN LINK 48TSSOP |

| LTC2440IGN#PBF | IC ADC DIFFER 24-BIT HS 16-SSOP |

| VE-B1T-MX-F1 | CONVERTER MOD DC/DC 6.5V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7328BRUZ | 制造商:Analog Devices 功能描述:A/D Converter (A-D) IC |

| AD7328BRUZ-REEL | 功能描述:IC ADC 12BIT+SAR 8CHAN 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:iCMOS® 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7328BRUZ-REEL7 | 功能描述:IC ADC 12BIT+ SAR 8CHAN 20TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:iCMOS® 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7329 | 制造商:AD 制造商全称:Analog Devices 功能描述:1 MSPS, 8-Channel, Software-Selectable, True Bipolar Input, 12-Bit Plus Sign ADC |

| AD7329BRUZ | 功能描述:IC ADC 12BIT 8CH MUX SPI 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

发布紧急采购,3分钟左右您将得到回复。