- 您现在的位置:买卖IC网 > PDF目录10222 > AD7472BRUZ (Analog Devices Inc)IC ADC 12BIT PARALLEL 24TSSOP PDF资料下载

参数资料

| 型号: | AD7472BRUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/21页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT PARALLEL 24TSSOP |

| 标准包装: | 62 |

| 位数: | 12 |

| 采样率(每秒): | 1.5M |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 12mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 管件 |

| 输入数目和类型: | 1 个单端,单极 |

REV. B

AD7470/AD7472

–17–

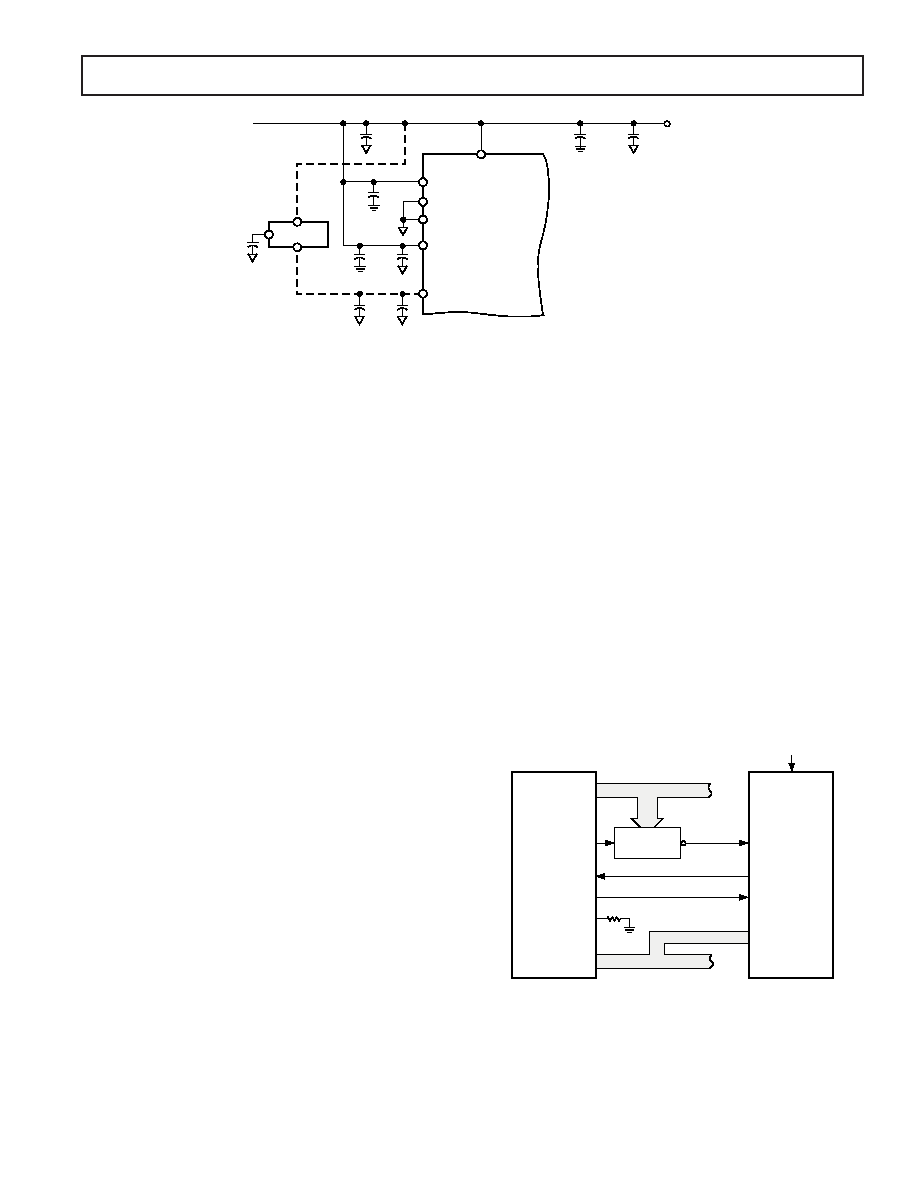

GROUNDING AND LAYOUT

The analog and digital power supplies are independent and

separately pinned out to minimize coupling between the analog

and digital sections within the device. To complement the excel-

lent noise performance of the AD7470/AD7472, it is imperative

that care be given to the PCB layout. Figure 16 shows a recom-

mended connection diagram for the AD7470/AD7472.

All of the AD7470/AD7472 ground pins should be soldered

directly to a ground plane to minimize series inductance. The

AVDD, DVDD, and VDRIVE pins should be decoupled to both the

analog and digital ground planes. The large value capacitors will

decouple low frequency noise to analog ground; the small value

capacitors will decouple high frequency noise to digital ground.

All digital circuitry power pins should be decoupled to the

digital ground plane. The use of ground planes can physically

separate sensitive analog components from the noisy digital

system. The two ground planes should be joined in only one

place and should not overlap so as to minimize capacitive

coupling between them. If the AD7470/AD7472 is in a

system where multiple devices require AGND to DGND

connections, the connection should still be made at one point

only, a star ground point, which should be established as close

as possible to the AD7470/AD7472.

Noise can be minimized by applying some simple rules to the

PCB layout: analog signals should be kept away from digital

signals; fast switching signals like clocks should be shielded with

digital ground to avoid radiating noise to other sections of the

board and clock signals should never be run near the analog

inputs; avoid running digital lines under the device as these will

couple noise onto the die; the power supply lines to the AD7470/

AD7472 should use as large a trace as possible to provide a low

impedance path and reduce the effects of glitches on the power

supply line; avoid crossover of digital and analog signals and

place traces that are on opposite sides of the board at right angles

to each other.

Noise to the analog power line can be further reduced by use of

multiple decoupling capacitors as shown in Figure 16. Decou-

pling capacitors should be placed directly at the power inlet to

the PCB and also as close as possible to the power pins of the

AD7470/AD7472. The same decoupling method should be

used on other ICs on the PCB, with the capacitor leads as short

as possible to minimize lead inductance.

POWER SUPPLIES

Separate power supplies for AVDD and DVDD are desirable but,

if necessary, DVDD may share its power connection to AVDD.

The digital supply (DVDD) must not exceed the analog supply

(AVDD) by more than 0.3 V in normal operation.

MICROPROCESSOR INTERFACING

AD7470/AD7472 to ADSP-2185 Interface

Figure 17 shows a typical interface between the AD7470/AD7472

and the ADSP-2185. The ADSP-2185 processor can be used in

one of two memory modes, full memory mode and host mode.

The Mode C pin determines in which mode the processor works.

The interface in Figure 17 is set up to have the processor work-

ing in full memory mode, which allows full external addressing

capabilities.

When the AD7470/AD7472 has finished converting, the BUSY

line requests an interrupt through the

IRQ2 pin. The IRQ2

interrupt has to be set up in the interrupt control register as

edge-sensitive. The

DMS (data memory select) pin latches in

the address of the ADC into the address decoder. The read

operation is thus started.

ADDRESS

DECODER

AD7470/

AD7472*

ADSP-2185*

A0–A15

DMS

IRQ2

RD

MODE C

D0–D23

CONVST

CS

RD

BUSY

DB0–DB9

(DB11)

ADDRESS BUS

DATA BUS

100k

*ADDITIONAL PINS OMITTED FOR CLARITY

OPTIONAL

Figure 17. Interfacing to the ADSP-2185

AD7470/AD7472 to ADSP-21065 Interface

Figure 18 shows a typical interface between the AD7470/AD7472

and the ADSP-21065L SHARC

processor. This interface is an

example of one of three DMA handshake modes. The

MSX

AD7470/

AD7472

AD780

10 F

+

1nF

VIN

VOUT

1nF

+

10 F

0.1 F

10 F

DVDD

AGND

DGND

VDRIVE

VREF

AVDD

+

0.1 F47 F

ANALOG

SUPPLY

5V

+

0.1 F

Figure 16. Decoupling Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| GTC06A-16S-1P | CONN PLUG 7POS STRAIGHT W/PINS |

| VI-B13-MY | CONVERTER MOD DC/DC 24V 50W |

| VE-2NM-CU-F1 | CONVERTER MOD DC/DC 10V 200W |

| 14282-20PG-300 | CONN RCPT 20POS PNL MNT PIN |

| SP3243EBEY-L/TR | IC TXRX RS232 INTELLIGNT 28TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7472BRUZ-REEL | 功能描述:IC ADC 12BIT PARALLEL 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7472BRUZ-REEL7 | 功能描述:IC ADC 12BIT PARALLEL 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7472BRZ | 功能描述:IC ADC 12BIT PARALLEL 24SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7472YR | 制造商:Analog Devices 功能描述:ADC Single SAR 1.5Msps 12-bit Parallel 24-Pin SOIC W 制造商:Rochester Electronics LLC 功能描述:12 BIT 1.5MSPS PARALLEL ADC I.C. - Bulk |

| AD7472YR-REEL | 功能描述:IC ADC 12BIT PARALLEL 24-SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

发布紧急采购,3分钟左右您将得到回复。