- 您现在的位置:买卖IC网 > PDF目录10228 > AD7685CRMZRL7 (Analog Devices Inc)IC ADC 16BIT PSEUDO-DIFF 10MSOP PDF资料下载

参数资料

| 型号: | AD7685CRMZRL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/28页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT PSEUDO-DIFF 10MSOP |

| 产品培训模块: | Power Line Monitoring Motor Control |

| 设计资源: | Parametric Measurement Unit and Supporting Components for PAD Appls Using AD5522 and AD7685 (CN0104) Integrated Device Power Supply for PAD with Output Voltage Range 0 V to 25 V (CN0130) |

| 标准包装: | 1,000 |

| 系列: | PulSAR® |

| 位数: | 16 |

| 采样率(每秒): | 250k |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 15mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-TFSOP,10-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 10-MSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 1 个伪差分,单极 |

| 配用: | EVAL-AD7685CBZ-ND - BOARD EVAL FOR AD7685 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD7685

Rev. C | Page 22 of 28

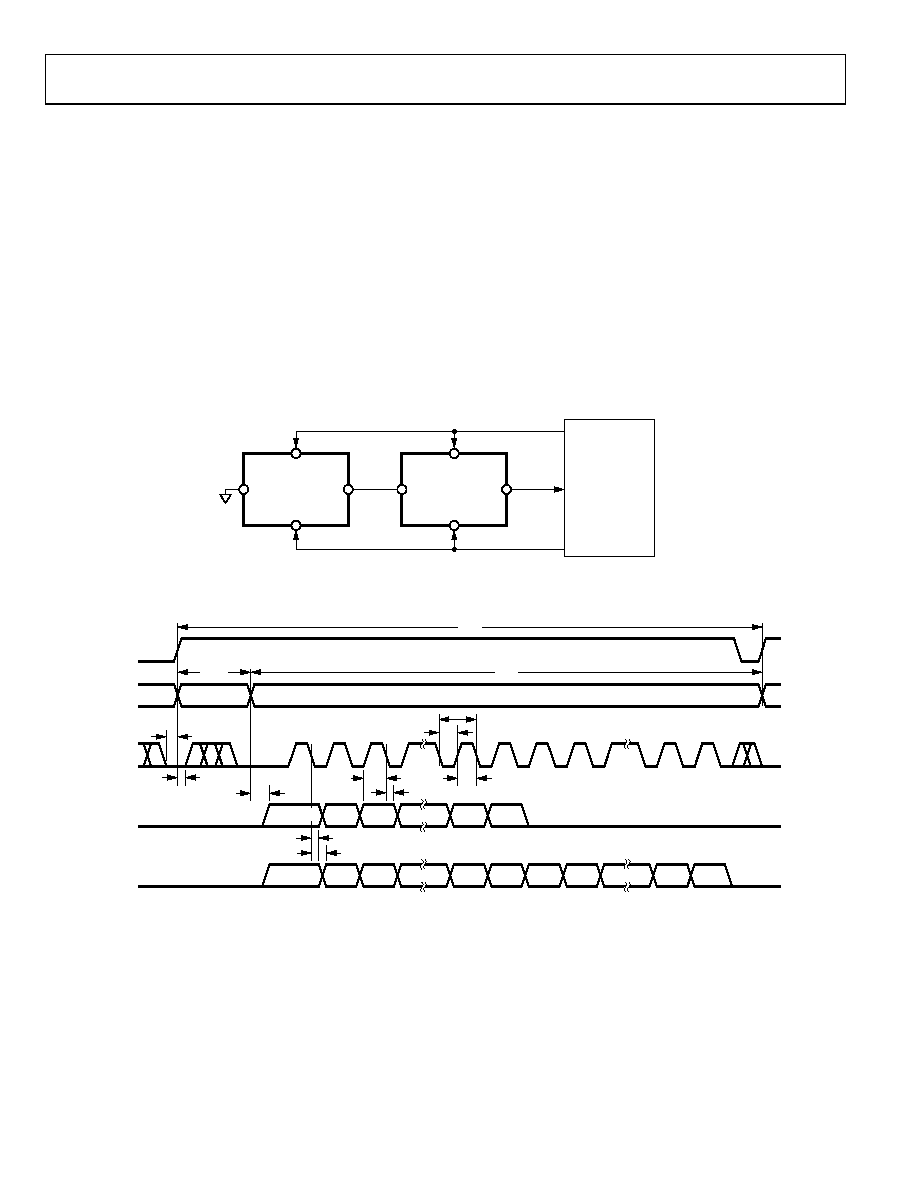

CHAIN MODE, NO BUSY INDICATOR

This mode can be used to daisy-chain multiple AD7685s on a

3-wire serial interface. This feature is useful for reducing

component count and wiring connections, for example, in

isolated multiconverter applications or for systems with a

limited interfacing capacity. Data readback is analogous to

clocking a shift register.

A connection diagram example using two AD7685s is shown in

When SDI and CNV are low, SDO is driven low. With SCK low,

a rising edge on CNV initiates a conversion and selects the

chain mode. In this mode, CNV is held high during the

conversion phase and the subsequent data readback. When the

conversion is complete, the MSB is output onto SDO and the

AD7685 enters the acquisition phase and powers down. The

remaining data bits stored in the internal shift register are then

clocked by subsequent SCK falling edges. For each ADC, SDI

feeds the input of the internal shift register and is clocked by the

SCK falling edge. Each ADC in the chain outputs its data MSB

first, and 16 × N clocks are required to readback the N ADCs.

The data is valid on both SCK edges. Although the rising edge

can be used to capture the data, a digital host using the SCK

falling edge will allow a faster reading rate and, consequently,

more AD7685s in the chain, provided the digital host has an

acceptable hold time. The maximum conversion rate may be

reduced due to the total readback time. For instance, with a 5 ns

digital host setup time and 3 V interface, up to eight AD7685s

running at a conversion rate of 220 kSPS can be daisy-chained

on a 3-wire port.

CLK

CONVERT

DATA IN

DIGITAL HOST

02

96

8-

0

40

CNV

SCK

SDO

SDI

AD7685

B

CNV

SCK

SDO

SDI

AD7685

A

Figure 42. Chain Mode Connection Diagram

SDOA = SDIB

DA15

DA14

DA13

SCK

1

2

3

303132

tSSDISCK

tHSDISCK

tEN

CONVERSION

ACQUISITION

tCONV

tCYC

tACQ

ACQUISITION

CNV

DA1

14

15

tSCK

tSCKL

tSCKH

DA0

17

18

16

SDIA = 0

SDOB

DB15

DB14

DB13

DA1

DB1DB0DA15

DA14

tHSDO

tDSDO

tSSCKCNV

tHSCKCNV

DA0

02

96

8-

0

41

Figure 43. Chain Mode Serial Interface Timing

相关PDF资料 |

PDF描述 |

|---|---|

| ADM4852ARZ-REEL7 | IC TXRX RS485/422 2.5MBPS 8SOIC |

| AD7714ARSZ-3REEL | IC ADC 24BIT SIGMA-DELTA 28SSOP |

| SP490CN-L/TR | IC TXRX RS485 FULL DUPLEX 8NSOIC |

| SP1485EMN-L/TR | IC TXRX RS485 DIFF ESD 8SOIC |

| LTC1745IFW#PBF | IC ADC 12BIT 25MSPS LN 48TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7685-C-U2 | 制造商:Analog Devices 功能描述:250 KSPS 16-BIT PULSAR? A/D CONVERTER IN ?SOIC - Bulk |

| AD7685-S-U2 | 制造商:Analog Devices 功能描述:250 KSPS 16-BIT PULSAR? A/D CONVERTER - Bulk |

| AD7685XRM-U3 | 制造商:Analog Devices 功能描述:A/D CONVERTER 250KSPS 16-BIT PULSAR - Bulk |

| AD7686 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, +/-0.65 LSB INL, 500 kSPS PulSAR Differential ADC in MSOP/QFN |

| AD76861 | 制造商:AD 制造商全称:Analog Devices 功能描述:18-Bit, 2 MSPS PulSAR 15 mW ADC in LFCSP (QFN) |

发布紧急采购,3分钟左右您将得到回复。