- 您现在的位置:买卖IC网 > PDF目录10064 > AD7711AQ (Analog Devices Inc)IC ADC 24BIT RTD I SOURCE 24CDIP PDF资料下载

参数资料

| 型号: | AD7711AQ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/28页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT RTD I SOURCE 24CDIP |

| 标准包装: | 15 |

| 位数: | 24 |

| 采样率(每秒): | 1.03k |

| 数据接口: | 串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 52.5mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 80°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 24-CDIP(0.300",7.62mm) |

| 供应商设备封装: | 24-CDIP |

| 包装: | 管件 |

| 输入数目和类型: | 1 个单端,单极;1 个单端,双极;1 个差分,单极;1 个差分,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页

2

REV.G

AD7711

–5–

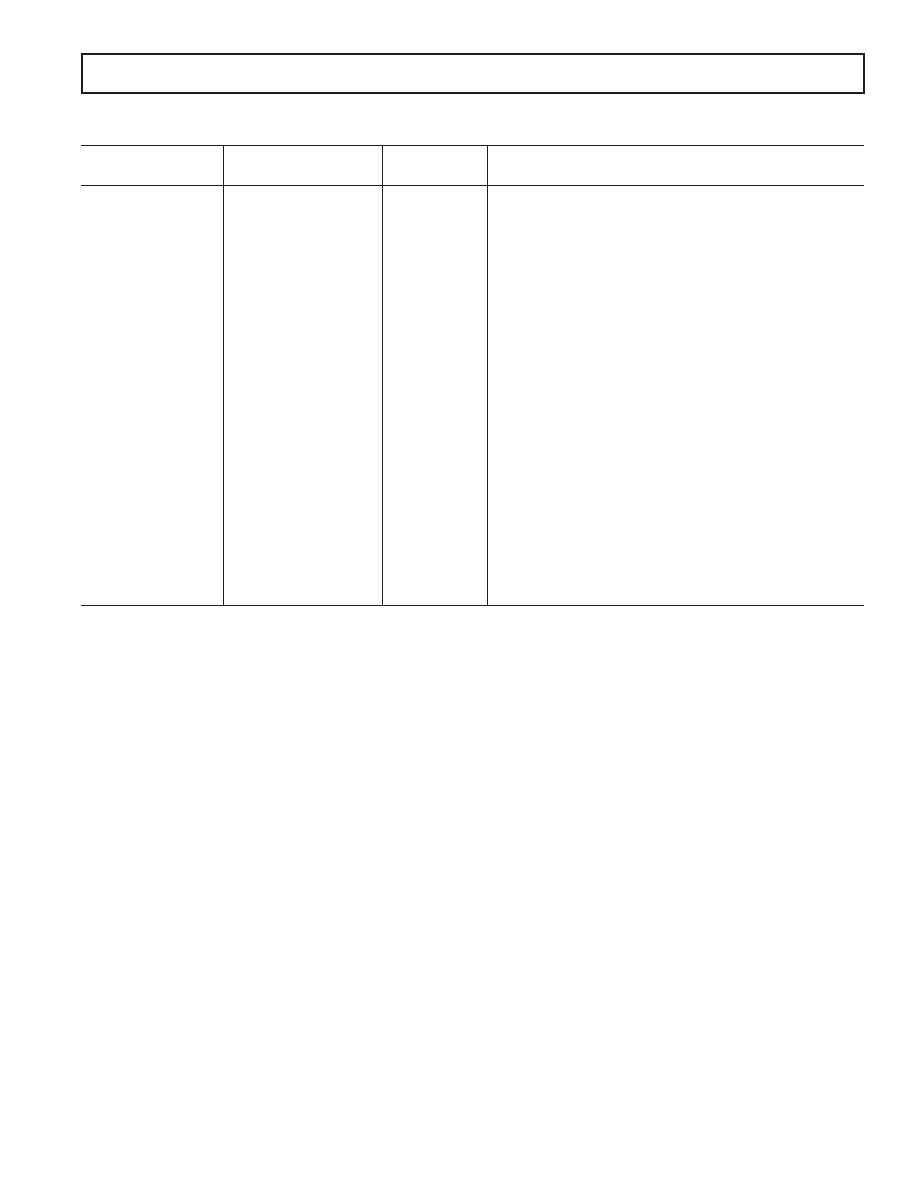

TIMING CHARACTERISTICS1, 2

Limit at TMIN, TMAX

Parameter

(A, S Versions)

Unit

Conditions/Comments

fCLK IN

4, 5

400

kHz min

Master Clock Frequency: Crystal Oscillator or Externally

Supplied for Specified Performance

10

MHz max

tCLK IN LO

0.4

× t

CLK IN

ns min

Master Clock Input Low Time; tCLK IN = 1/fCLK IN

tCLK IN HI

0.4

× tCLK IN

ns min

Master Clock Input High Time

tr

6

50

ns max

Digital Output Rise Time. Typically 20 ns

tf

6

50

ns max

Digital Output Fall Time. Typically 20 ns

t1

1000

ns min

SYNC Pulse Width

Self-Clocking Mode

t2

0

ns min

DRDY to RFS Setup Time

t3

0

ns min

DRDY to RFS Hold Time

t4

2

× t

CLK IN

ns min

A0 to

RFS Setup Time

t5

0

ns min

A0 to

RFS Hold Time

t6

4

× tCLK IN + 20

ns max

RFS Low to SCLK Falling Edge

t7

7

4

× t

CLK IN + 20

ns max

Data Access Time (

RFS Low to Data Valid)

t8

7

tCLK IN/2

ns min

SCLK Falling Edge to Data Valid Delay

tCLK IN/2 + 30

ns max

t9

tCLK IN/2

ns nom

SCLK High Pulse Width

t10

3

× t

CLK IN/2

ns nom

SCLK Low Pulse Width

t14

50

ns min

A0 to

TFS Setup Time

t15

0

ns min

A0 to

TFS Hold Time

t16

4

× t

CLK IN + 20

ns max

TFS to SCLK Falling Edge Delay Time

t17

4

× tCLK IN

ns min

TFS to SCLK Falling Edge Hold Time

t18

0

ns min

Data Valid to SCLK Setup Time

t19

10

ns min

Data Valid to SCLK Hold Time

NOTES

1Guaranteed by design, not production tested. All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2See Figures 10 to 13.

3The AD7711 is specified with a 10 MHz clock for AV

DD voltages of 5 V

± 5%. It is specified with an 8 MHz clock for AV

DD voltages greater than 5.25 V and less

than 10.5 V.

4CLK IN duty cycle range is 45% to 55%. CLK IN must be supplied whenever the AD7711 is not in STANDBY mode. If no clock is present in this case, the device

can draw higher current than specified and possibly become uncalibrated.

5The AD7711 is production tested with f

CLK IN at 10 MHz (8 MHz for AVDD > 5.25 V). It is guaranteed by characterization to operate at 400 kHz.

6Specified using 10% and 90% points on waveform of interest.

7These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross 0.8 V or 2.4 V.

(DVDD = +5 V

5%; AVDD = +5 V or +10 V

3

5%; VSS = 0 V or –5 V

10%; AGND = DGND =

0 V; fCLK IN = 10 MHz; Input Logic 0 = 0 V, Logic 1 = DVDD, unless otherwise noted.)

相关PDF资料 |

PDF描述 |

|---|---|

| LTC486CSW | IC DVR RS485 LOW PWR QUAD 16SOIC |

| IDT72231L25JI | IC FIFO SYNC 512X9 25NS 32PLCC |

| LTC2221CUP#PBF | IC ADC 12-BIT 135MSPS 64-QFN |

| MS27467E17A26SB | CONN PLUG 26POS STRAIGHT W/SCKT |

| MS27473T24A61PD | CONN PLUG 61POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7711AR | 功能描述:IC ADC 24BIT RTD I SOURCE 24SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD7711AR-REEL | 功能描述:IC ADC 24BIT RTD I SOURCE 24SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD7711AR-REEL7 | 功能描述:IC ADC 24BIT RTD I SOURCE 24SOIC RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD7711ARZ | 功能描述:IC ADC 24BIT RTD I SOURCE 24SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:microPOWER™ 位数:8 采样率(每秒):1M 数据接口:串行,SPI? 转换器数目:1 功率耗散(最大):- 电压电源:模拟和数字 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:24-VFQFN 裸露焊盘 供应商设备封装:24-VQFN 裸露焊盘(4x4) 包装:Digi-Reel® 输入数目和类型:8 个单端,单极 产品目录页面:892 (CN2011-ZH PDF) 其它名称:296-25851-6 |

| AD7711ARZ | 制造商:Analog Devices 功能描述:LC 2MOS SIGNAL CONDITIONING ANALOG/DIGIT |

发布紧急采购,3分钟左右您将得到回复。