- 您现在的位置:买卖IC网 > PDF目录10212 > AD7853LARS (Analog Devices Inc)IC ADC 12BIT SRL 200KSPS 24-SSOP PDF资料下载

参数资料

| 型号: | AD7853LARS |

| 厂商: | Analog Devices Inc |

| 文件页数: | 18/34页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT SRL 200KSPS 24-SSOP |

| 标准包装: | 59 |

| 位数: | 12 |

| 采样率(每秒): | 100k |

| 数据接口: | 8051,QSPI?,串行,SPI? µP |

| 转换器数目: | 2 |

| 功率耗散(最大): | 33mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 24-SSOP |

| 包装: | 管件 |

| 输入数目和类型: | 1 个伪差分,单极;1 个伪差分,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

REV. B

–25–

AD7853/AD7853L

high after the 16th SCLK rising edge as shown by the dotted

SYNC line in Figure 36. Thus a frame sync that gives a high

pulse, of one SCLK cycle minimum duration, at the beginning

of the read/write operation may be used. The rising edge of

SYNC enables the three-state on the DOUT pin. The falling

edge of

SYNC disables the three-state on the DOUT pin, and

data is clocked out on the falling edge of SCLK. Once

SYNC

goes high, the three-state on the DOUT pin is enabled. The

data input is sampled on the rising edge of SCLK and thus has

to be valid a time, t7, before this rising edge. The POLARITY

pin may be used to change the SCLK edge which the data is

sampled on and clocked out on. If resetting the interface is

required, the

SYNC must be taken high and then low.

Modes 4 and 5 (Self-Clocking Modes)

The timing diagrams in Figure 38 and Figure 39 are for Inter-

face Modes 4 and 5. Interface Mode 4 has a noncontinuous

SCLK output and Interface Mode 5 has a continuous SCLK

output. These modes of operation are especially different to all

the other modes since the SCLK and

SYNC are outputs. The

SYNC is generated by the part as is the SCLK. The master

clock at the CLKIN pin is routed directly to the SCLK pin for

Interface Mode 5 (Continuous SCLK) and the CLKIN signal is

gated with the

SYNC to give the SCLK (noncontinuous) for

Interface Mode 4.

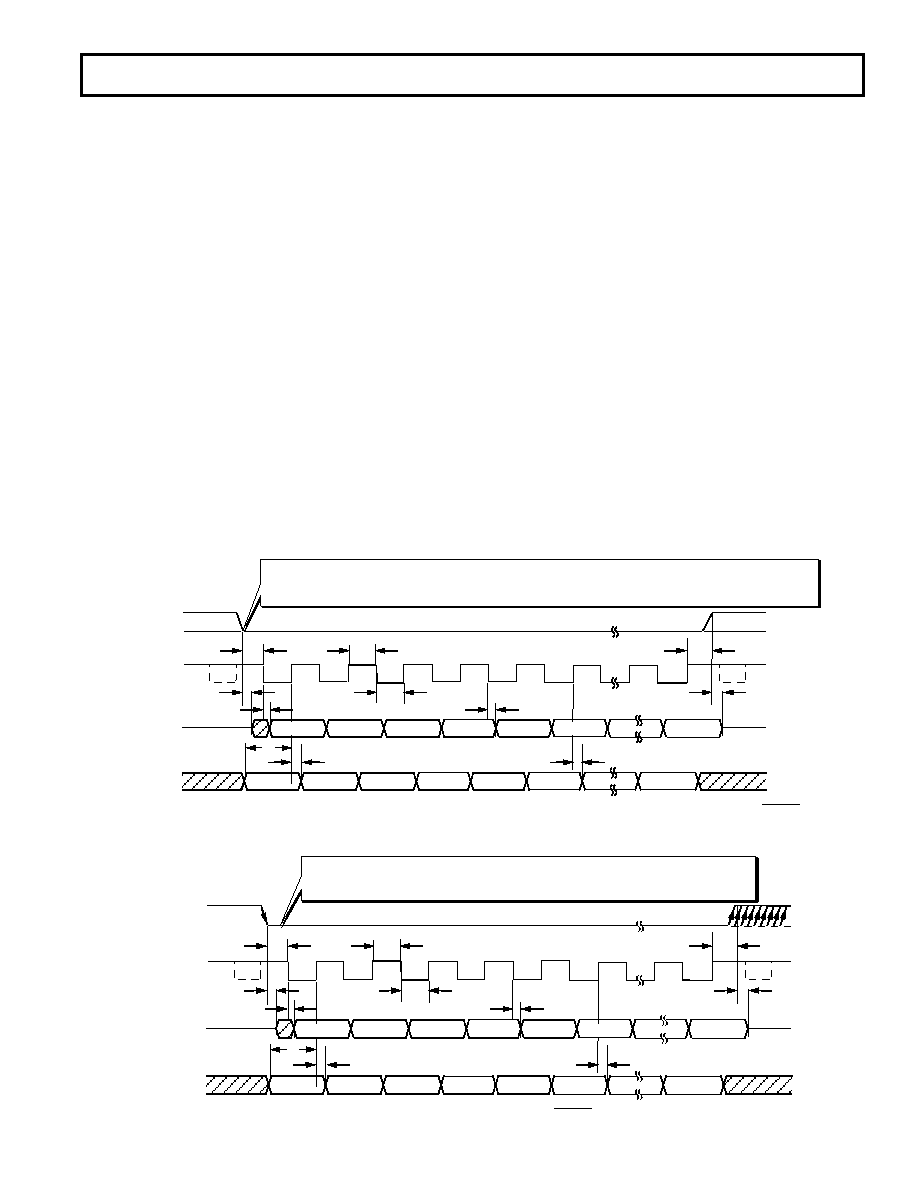

Mode 2 (3-Wire SPI/QSPI Interface Mode)

This is the DEFAULT INTERFACE MODE.

In Figure 35 below we have the timing diagram for Interface

Mode 2 which is the SPI/QSPI interface mode. Here the

SYNC

input is active low and may be pulsed or tied permanently low.

If

SYNC is permanently low 16 clock pulses must be applied to

the SCLK pin for the part to operate correctly, and with a

pulsed

SYNC input a continuous SCLK may be applied provided

SYNC is low for only 16 SCLK cycles. In Figure 30 the SYNC

going low disables the three-state on the DOUT pin. The first

falling edge of the SCLK after the

SYNC going low clocks out

the first leading zero on the DOUT pin. The DOUT pin is

three-stated again a time t12 after the SYNC goes high. With the

DIN pin the data input has to be set up a time, t7, before the

SCLK rising edge as the part samples the input data on the

SCLK rising edge in this case. The POLARITY pin may be

used to change the SCLK edge which the data is sampled on

and clocked out on. If resetting the interface is required, the

SYNC must be taken high and then low.

Mode 3 (QSPI Interface Mode)

Figure 36 shows the timing diagram for Interface Mode 3. In

this mode the DSP is the master and the part is the slave. Here

the

SYNC input is edge triggered from high to low, and the 16

clock pulses are counted from this edge. Since the clock pulses

are counted internally then the

SYNC signal does not have to go

t

3 = –0.4 tCLKIN MIN (NONCONTINUOUS SCLK) –/+0.4 tSCLK MIN/MAX (CONTINUOUS SCLK),

t

6 = 75/115 MAX (5V/3V), t7 = 40/60ns MIN (5V/3V), t8 = 20/30 MIN (5V/3V),

t

11 = 20/30 MIN (NONCONTINUOUS SCLK) (5V/3V), (30/50)/0.4 tSCLK = ns MIN/MAX (CONTINUOUS SCLK) (5V/3V)

DOUT (O/P)

SCLK (I/P)

SYNC (I/P)

DB0

t

3

t

8

t

10

t

9

t

5

DIN (I/P)

THREE-

STATE

THREE-

STATE

t

11

t

6

t

6

t

8

16

23

4

5

16

POLARITY PIN

LOGIC HIGH

t

12

DB11

DB10

DB15

DB14

DB13

DB12

DB0

DB11

DB10

DB15

DB14

DB13

DB12

t

7

Figure 35. SPI/QSPI Mode 2 Timing Diagram for Read/Write Operation with DIN Input, DOUT Output and SYNC Input

(SM1 = SM2 = 0)

t

7

DOUT (O/P)

SCLK (I/P)

SYNC (I/P)

DB0

t

3

t

8

t

10

t

9

t

5

DIN (I/P)

THREE-

STATE

THREE-

STATE

t

11

t

6

t

6

t

8

16

23

4

5

16

POLAR PIN

LOGIC HIGHITY

t

12

DB11

DB10

DB15

DB14

DB13

DB12

DB0

DB11

DB10

DB15

DB14

DB13

DB12

t

3 = –0.4 tCLKIN MIN (NONCONTINUOUS SCLK) –/+0.4 tSCLK MIN/MAX (CONTINUOUS SCLK),

t

6 = 75/115 MAX (5V/3V), t7 = 40/60ns MIN (5V/3V), t8 = 20/30 MIN (5V/3V),

t

11 = 20/30 MIN (5V/3V)

Figure 36. QSPI Mode 3 Timing Diagram for Read/Write Operation with SYNC Input Edge Triggered (SM1 = 0, SM2 = 1)

相关PDF资料 |

PDF描述 |

|---|---|

| GTC030-16S-1P | CONN RCPT 7POS PANEL MNT W/PINS |

| AD7719BR-REEL7 | IC ADC 16BIT 24BIT DUAL 28-SOIC |

| MS27484T12F3SD | CONN PLUG 3POS STRAIGHT W/SCKT |

| SP3088EEN-L/TR | IC TXRX RS485/RS422 ESD 8NSOIC |

| AD7951BCPZRL | IC ADC 14BIT 1MSPS 48-LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7853LARS-REEL | 功能描述:IC ADC 12BIT SRL 200KSPS 24-SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7853LARSZ | 功能描述:IC ADC 12BIT SRL 200KSPS 24SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7853LARSZ-REEL | 功能描述:IC ADC 12BIT SRL 200KSPS 24SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

| AD7853LARZ | 功能描述:IC ADC 12BIT SRL 200KSPS 24SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD7853LARZ-REEL | 功能描述:IC ADC 12BIT SRL 200KSPS 24SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:12 采样率(每秒):3M 数据接口:- 转换器数目:- 功率耗散(最大):- 电压电源:- 工作温度:- 安装类型:表面贴装 封装/外壳:SOT-23-6 供应商设备封装:SOT-23-6 包装:带卷 (TR) 输入数目和类型:- |

发布紧急采购,3分钟左右您将得到回复。