参数资料

| 型号: | AD8195ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/20页 |

| 文件大小: | 0K |

| 描述: | IC BUFF HDMI/DVI W/EQUAL 40LFCSP |

| 标准包装: | 1 |

| 功能: | 开关 |

| 电路: | 1 x 1:1 |

| 电压电源: | 单电源 |

| 电压 - 电源,单路/双路(±): | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-VQ(6x6) |

| 包装: | 托盘 |

AD8195

Data Sheet

Rev. B | Page 18 of 20

TMDS Terminations

The AD8195 provides internal 50 single-ended terminations

for all of its high speed inputs and outputs. It is not necessary to

include external termination resistors for the TMDS differential

pairs on the PCB.

The output termination resistors of the AD8195 back terminate

the output TMDS transmission lines. These back terminations

act to absorb reflections from impedance discontinuities on the

output traces, improving the signal integrity of the output traces

and adding flexibility to how the output traces can be routed.

For example, interlayer vias can be used to route the AD8195

TMDS outputs on multiple layers of the PCB without severely

degrading the quality of the output signal.

Auxiliary Control Signals

There are three single-ended control signals associated with

each source or sink in an HDMI/DVI application. These are

CEC and two DDC lines. The two signals on the DDC bus are

SDA and SCL (serial data and serial clock, respectively). These

three signals can be buffered through the AD8195 and do not

need to be routed with the same strict considerations as the

high speed TMDS signals.

In general, it is sufficient to route each auxiliary signal as a

single-ended trace. These signals are not sensitive to impedance

discontinuities, do not require a reference plane, and can be

routed on multiple layers of the PCB. However, it is best to

follow strict layout practices whenever possible to prevent the

PCB design from affecting the overall application. The specific

routing of the CEC and DDC lines depends on the application

in which the AD8195 is being used.

For example, the maximum speed of signals present on the

auxiliary lines is 100 kHz I2C data on the DDC lines; therefore,

any layout that enables 100 kHz I2C to be passed over the DDC

bus should suffice. The HDMI specification, however, places a

strict 50 pF limit on the amount of capacitance that can be

measured on either SDA or SCL at the HDMI input connector.

This 50 pF limit includes the HDMI connector, the PCB, and

whatever capacitance is seen at the input of the AD8195. There

is a similar limit of 150 pF of input capacitance for the CEC line.

The parasitic capacitance of traces on a PCB increases with

trace length. To help ensure that a design satisfies the HDMI

specification, the length of the CEC and DDC lines on the PCB

should be made as short as possible. Additionally, if there is a

reference plane in the layer adjacent to the auxiliary traces in

the PCB stack-up, relieving or clearing out this reference plane

immediately under the auxiliary traces significantly decreases

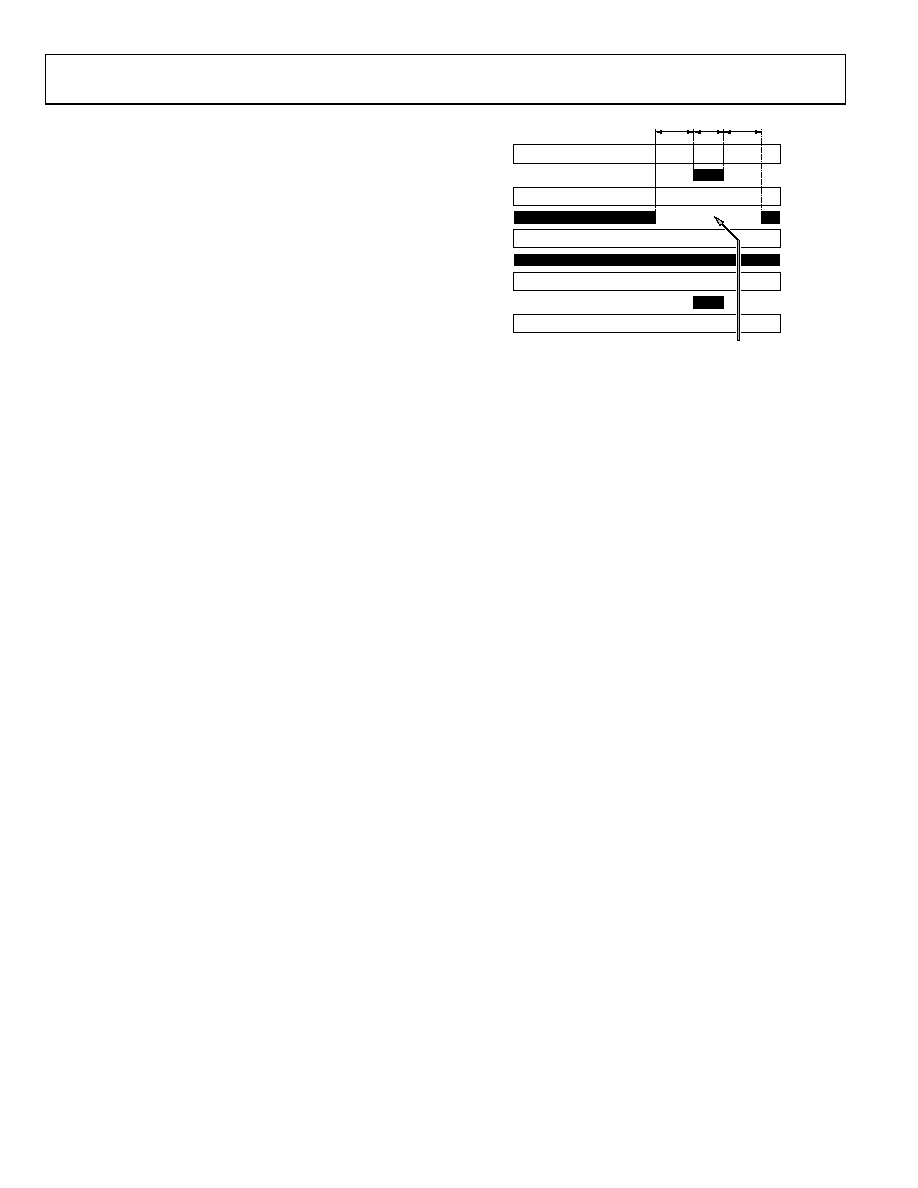

the amount of parasitic trace capacitance. An example of the

board stack-up is shown in Figure 35.

The AD8195 buffers the auxiliary signals; therefore, only the

input traces, connector, and AD8195 input capacitance must be

considered when designing a PCB to meet HDMI specifications.

PCB DIELECTRIC

LAYER 1: MICROSTRIP

SILKSCREEN

PCB DIELECTRIC

LAYER 2: REFERENCE PLANE

LAYER 3: REFERENCE PLANE

LAYER 4: MICROSTRIP

W

3W

REFERENCE LAYER

RELIEVED UNDERNEATH

MICROSTRIP

07049-

009

Figure 35. Example Board Stack-Up

Power Supplies

The AD8195 has four separate power supplies referenced to a

single ground, AVEE. The supply/ground pairs are

AVCC/AVEE

VTTI/AVEE

VTTO/AVEE

AMUXVCC/AVEE.

The AVCC/AVEE (3.3 V) supply powers the core of the AD8195.

The VTTI/AVEE supply (3.3 V) powers the input termination

(see Figure 30). Similarly, the VTTO/AVEE supply (3.3 V)

powers the output termination (see Figure 31). The AMUXVCC/

AVEE supply (5 V) powers the auxiliary buffer core.

In a typical application, all pins labeled AVEE should be connected

directly to ground. All pins labeled AVCC, VTTI, or VTTO

should be connected to 3.3 V, and Pin AMUXVCC should be

tied to 5 V. The AVCC supply powers the TMDS buffers while

AMUXVCC powers the DDC/CEC buffers. The AMUXVCC

pin can be connected to the 5 V supply provided from the input

HDMI connector to ensure that the DDC and CEC buffers

remain functional when the system is powered off. The supplies

can also be powered individually, but care must be taken to

ensure that each stage of the AD8195 is powered correctly.

DDC Reference Inputs

The VREF_IN and VREF_OUT voltages (3.3 V to 5 V) provide

reference levels for the DDC buffers. Both voltages are referenced

to AVEE. The voltage applied at these reference inputs should

be the same as the pull-up voltage for corresponding DDC bus.

Unused DDC/CEC Buffers

If the DDC and the CEC buffers are not used, the AD8195 does

not require a 5 V supply for AMUXVCC. For operation without

the buffers, tie AMUXVCC to AVCC (nominally 3.3 V) and tie

VREF_IN and VREF_OUT to AVEE (nominally ground).

Other buffer pins can be left floating.

相关PDF资料 |

PDF描述 |

|---|---|

| AD8196ACPZ | IC SWITCH DVI/HDMI 2:1 56-LFCSP |

| AD8197AASTZ | IC HDMI/DVI SWITCH 4:1 100LQFP |

| AD8197ASTZ-RL | IC SWITCH DVI/HDMI 4:1 100-LQFP |

| AD8197BASTZ-RL | IC SWITCH DVI/HDMI 4:1 100-LQFP |

| AD8303ARZ-REEL | IC DAC 12BIT SERIAL 14SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8195ACPZ-R7 | 功能描述:IC BUFF HDMI/DVI W/EQUAL 40LFCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 模拟开关,多路复用器,多路分解器 系列:- 标准包装:1,000 系列:- 功能:多路复用器 电路:1 x 4:1 导通状态电阻:- 电压电源:双电源 电压 - 电源,单路/双路(±):±5V 电流 - 电源:7mA 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC 包装:带卷 (TR) |

| AD8195-EVALZ | 制造商:Analog Devices 功能描述:EVALUATION BOARD - Boxed Product (Development Kits) |

| AD8195XCPZ | 功能描述:IC BUFF HDMI/DVI W/EQUAL 40LFCSP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:上次购买时间 类型:HDMI/DVI 缓冲器 应用:HDTV 安装类型:表面贴装 封装/外壳:40-VFQFN 裸露焊盘,CSP 供应商器件封装:40-LFCSP-VQ(6x6) 标准包装:1 |

| AD8196 | 制造商:AD 制造商全称:Analog Devices 功能描述:2:1 HDMI/DVI Switch with Equalization |

| AD8196ACPZ | 功能描述:IC SWITCH DVI/HDMI 2:1 56-LFCSP RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。