- 您现在的位置:买卖IC网 > PDF目录6065 > AD8555ACPZ-REEL7 (Analog Devices Inc)IC AMP CHOPPER 2MHZ 10MA 16LFCSP PDF资料下载

参数资料

| 型号: | AD8555ACPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 13/28页 |

| 文件大小: | 0K |

| 描述: | IC AMP CHOPPER 2MHZ 10MA 16LFCSP |

| 标准包装: | 1 |

| 系列: | DigiTrim® |

| 放大器类型: | 断路器(零漂移) |

| 电路数: | 1 |

| 转换速率: | 1.2 V/µs |

| 增益带宽积: | 2MHz |

| 电流 - 输入偏压: | 16nA |

| 电压 - 输入偏移: | 2µV |

| 电流 - 电源: | 2mA |

| 电流 - 输出 / 通道: | 10mA |

| 电压 - 电源,单路/双路(±): | 2.7 V ~ 5.5 V |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-VQFN 裸露焊盘,CSP |

| 供应商设备封装: | 16-LFCSP-VQ |

| 包装: | 标准包装 |

| 产品目录页面: | 771 (CN2011-ZH PDF) |

| 其它名称: | AD8555ACPZ-REEL7DKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD8555

Rev. A | Page 20 of 28

04598-0-003

CODE

01

0

1

WAVEFORM

tW0

tWS

tW0

tWS

tW0

tWS

tW1

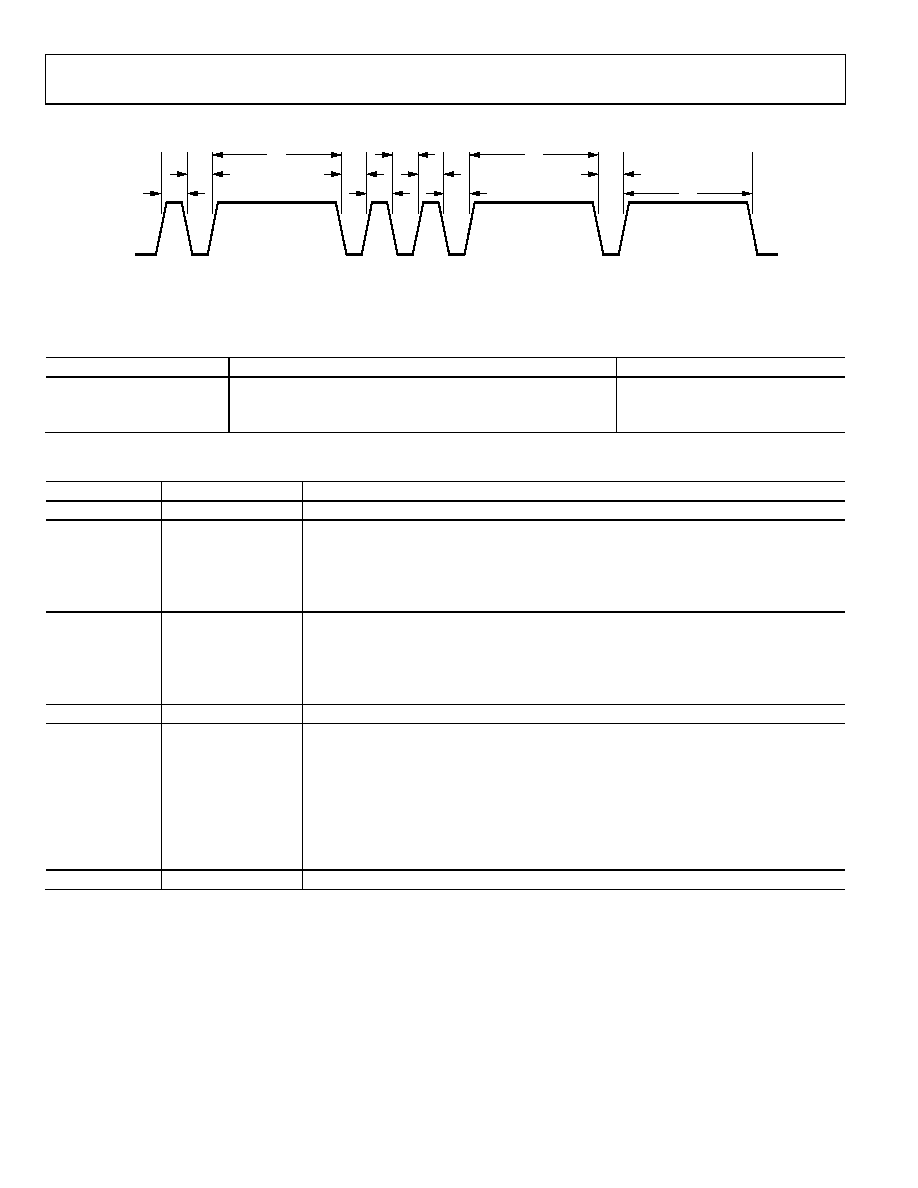

Figure 51. Timing Diagram for Code 010011

Table 10. Timing Specifications

Timing Parameter

Description

Specification

tw0

Pulse Width for Loading 0 into Shift Register

Between 50 ns and 10 μs

tw1

Pulse Width for Loading 1 into Shift Register

≥50 μs

tws

Width between Pulses

≥10 μs

Table 11. 38-Bit Serial Word Format

Field No.

Bits

Description

Field 0

Bits 0 to 11

12-Bit Start of Packet 1000 0000 0001

Field 1

Bits 12 to 13

2-Bit Function

00: Change Sense Current

01: Simulate Parameter Value

10: Program Parameter Value

11: Read Parameter Value

Field 2

Bits 14 to 15

2-Bit Parameter

00: Second Stage Gain Code

01: First Stage Gain Code

10: Output Offset Code

11: Other Functions

Field 3

Bits 16 to 17

2-Bit Dummy 10

Field 4

Bits 18 to 25

8-Bit Value

Parameter 00 (Second Stage Gain Code): 3 LSBs Used

Parameter 01 (First Stage Gain Code): 7 LSBs Used

Parameter 10 (Output Offset Code): All 8 Bits Used

Parameter 11 (Other Functions)

Bit 0 (LSB): Master Fuse

Bit 1: Fuse for Production Test at Analog Devices

Bit 2: Parity Fuse

Field 5

Bits 26 to 37

12-Bit End of Packet 0111 1111 1110

A 38-bit serial word is used, divided into 6 fields. Assuming

each bit can be loaded in 60 μs, the 38-bit serial word transfers

in 2.3 ms. Table 11 summarizes the word format.

Fields 0 and 5 are the start of packet and end of packet field,

respectively. Matching the start of packet field with 1000 0000

0001 and the end of packet field with 0111 1111 1110 ensures

that the serial word is valid and enables decoding of the other

fields. Field 3 breaks up the data and ensures that no data com-

bination can inadvertently trigger the start of packet and end of

packet fields. Field 0 should be written first and Field 5 written

last. Within each field, the MSB must be written first and the

LSB written last. The shift register features power-on reset to

minimize the risk of inadvertent programming; power-on reset

occurs when VDD is between 0.7 V and 2.2 V.

相关PDF资料 |

PDF描述 |

|---|---|

| TSW-109-08-G-S-RA | CONN HEADER 9POS .100 SGL R/A AU |

| AWH30A-0202-T-R | CONN HEADER 30POS RT ANG GOLD |

| TSW-122-07-T-S | CONN HEADER 22POS .100" SNGL TIN |

| AWH40G-0202-T-R | CONN HEADER 40POS VERT GOLD |

| TSW-122-06-T-S | CONN HEADER 22POS .100" SNGL TIN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD8555ACPZ-REEL71 | 制造商:AD 制造商全称:Analog Devices 功能描述:Zero-Drift, Digitally Programmable Sensor Signal Amplifier |

| AD8555AR | 制造商:Analog Devices 功能描述:SP Amp Current Sense Amp Single R-R I/O 5.5V 8-Pin SOIC N Tube 制造商:Analog Devices 功能描述:2.7V to 5.5V 1 2MHz vAv 8SOIC Bulk 制造商:Analog Devices 功能描述:AMP Z-DRIFT PROG GAIN 8555 SOIC8 |

| AD8555AR-EVAL | 制造商:Analog Devices 功能描述:Evaluation Board For Zero-Drift, Digitally Programmable Sensor Signal Amplifier |

| AD8555AR-REEL | 制造商:Analog Devices 功能描述:SP Amp Current Sense Amp Single R-R I/O 5.5V 8-Pin SOIC N T/R |

| AD8555AR-REEL7 | 制造商:Analog Devices 功能描述:SP Amp Current Sense Amp Single R-R I/O 5.5V 8-Pin SOIC N T/R |

发布紧急采购,3分钟左右您将得到回复。