- 您现在的位置:买卖IC网 > PDF目录10531 > AD9219ABCPZ-40 (Analog Devices Inc)IC ADC 10BIT SRL 40MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9219ABCPZ-40 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/56页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT SRL 40MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 10 |

| 采样率(每秒): | 40M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 4 |

| 功率耗散(最大): | 313mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 托盘 |

| 输入数目和类型: | 8 个单端,单极;4 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

AD9219

Data Sheet

Rev. E | Page 38 of 56

DEFAULT OPERATION AND JUMPER SELECTION

SETTINGS

The following is a list of the default and optional settings or

modes allowed on the AD9219 Rev. A evaluation board.

POWER: Connect the switching power supply that is

provided in the evaluation kit between a rated 100 V ac to

240 V ac wall outlet at 47 Hz to 63 Hz and P503.

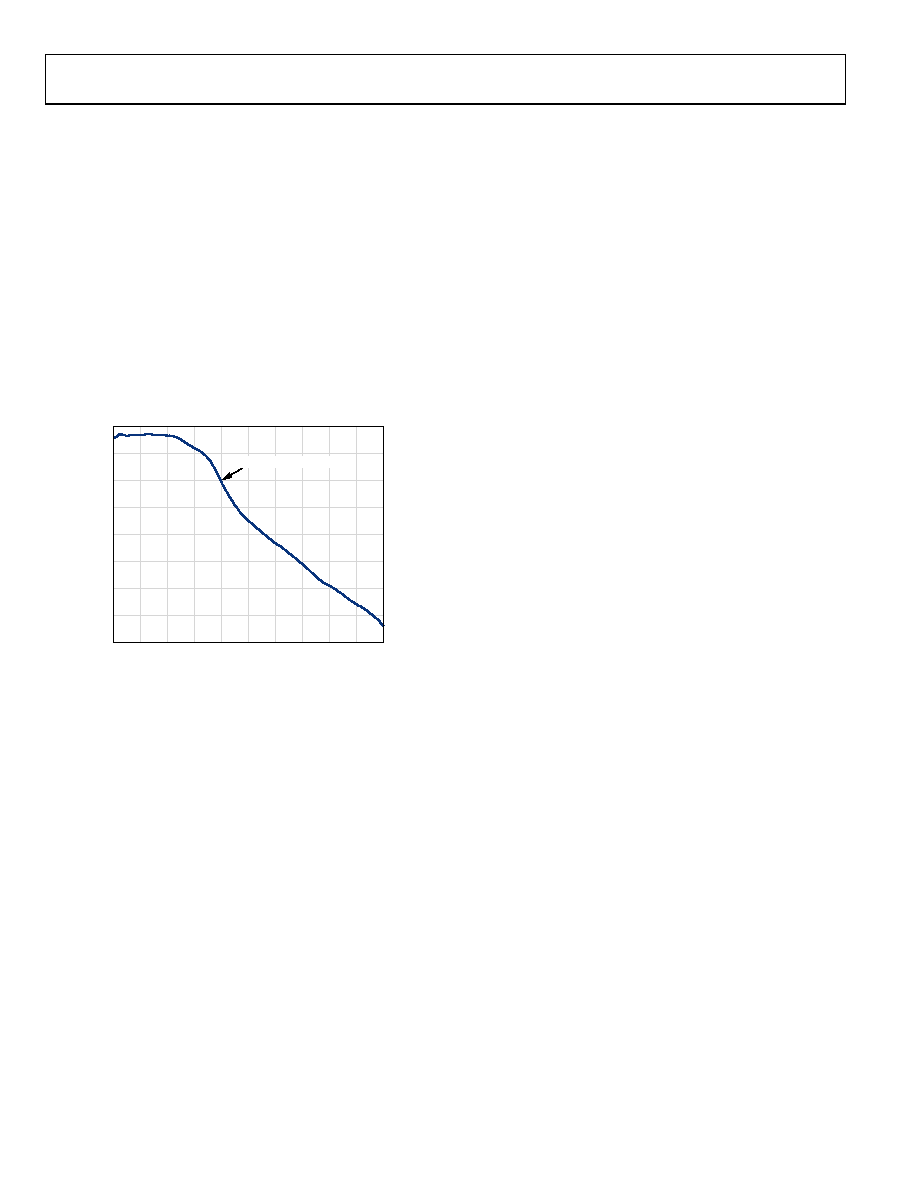

AIN: The evaluation board is set up for a transformer-

coupled analog input with an optimum 50 Ω impedance

match of 200 MHz of bandwidth (see Figure 72). For more

bandwidth response, the differential capacitor across the

analog inputs can be changed or removed. The common

mode of the analog inputs is developed from the center tap

of the transformer or AVDD_DUT/2.

0

AM

P

L

IT

UD

E

(

d

BF

S

)

FREQUENCY (MHz)

05

72

6-

0

85

0

–16

–14

–12

–10

–8

–6

–4

–2

50

100

150

200

250

300

350

400

450

500

–3dB CUTOFF = 200MHz

Figure 72. Evaluation Board Full-Power Bandwidth

VREF: VREF is set to 1.0 V by tying the SENSE pin to

ground, R237. This causes the ADC to operate in 2.0 V p-p

full-scale range. A separate external reference option using

the ADR510 is also included on the evaluation

board.

Populate R231 and R235 and remove C214. Proper use

of the VREF options is noted in the Voltage Reference

section.

RBIAS: RBIAS has a default setting of 10 kΩ (R201) to

ground and is used to set the ADC core bias current.

CLOCK: The default clock input circuitry is derived from a

simple transformer-coupled circuit using a high bandwidth

1:1 impedance ratio transformer (T201) that adds a very

low amount of jitter to the clock path. The clock input is

50 Ω terminated and ac-coupled to handle single-ended

sine wave types of inputs. The transformer converts the

single-ended input to a differential signal that is clipped

before entering the ADC clock inputs.

A differential LVPECL clock can also be used to clock

the ADC input using the AD9515 (U202). Populate R225

and R227 with 0 Ω resistors and remove R217 and R218 to

disconnect the default clock path inputs. In addition, populate

C207 and C208 with a 0.1 μF capacitor and remove C210

and C211 to disconnect the default clock path outputs. The

AD9515 has many pin-strappable options that are set to a

default mode of operation. Consult the AD9515 data sheet

for more information about these and other options.

In addition, an on-board oscillator is available on the OSC201

and can act as the primary clock source. The setup is quick

and involves installing R212 with a 0 Ω resistor and setting

the enable jumper (J205) to the on position. If the user wishes

to employ a different oscillator, two oscillator footprint options

are available (OSC201) to check the ADC performance.

PDWN: To enable the power-down feature, short J201 to

AVDD on the PDWN pin.

SCLK/DTP: To enable one of the two digital test patterns

on the digital outputs of the ADC, use J204. If J204 is tied to

AVDD during device power-up, Test Pattern 10 0000 0000 is

enabled. See the SCLK/DTP Pin section for details.

SDIO/ODM: To enable the low power, reduced signal option

(similar to the IEEE 1595.3 reduced range link LVDS output

standard), use J203. If J203 is tied to AVDD during device

power-up, it enables the LVDS outputs in a low power,

reduced signal option from the default ANSI-644 standard.

This option changes the signal swing from 350 mV p-p to

200 mV p-p, reducing the power of the DRVDD supply. See

the SDIO/ODM Pin section for more details.

CSB: To enable processing of the SPI information on the

SDIO and SCLK pins, tie J202 low in the always enable

mode. To ignore the SDIO and SCLK information, tie J202

to AVDD.

Non-SPI Mode: For users who wish to operate the DUT

without using SPI, remove Jumpers J302, J303, and J304.

This disconnects the CSB, SCLK/DTP, and SDIO/ODM pins

from the control bus, allowing the DUT to operate in its

simplest mode. Each of these pins has internal termination

and will float to its respective level.

D + x, D x: If an alternative data capture method to the setup

shown in Figure 73 is used, optional receiver terminations,

R206 to R211, can be installed next to the high speed back-

plane connector.

相关PDF资料 |

PDF描述 |

|---|---|

| MS3101A12S-3S | CONN RCPT 2POS FREE HNG W/SCKT |

| AD7686CRMZ | IC ADC 16BIT 500KSPS 10MSOP |

| VI-J41-MW-F2 | CONVERTER MOD DC/DC 12V 100W |

| AD7864ASZ-2 | IC ADC 12BIT PAR 520K 4CH 44MQFP |

| PT06A-14-15S | CONN PLUG 15POS W/SOCKETS SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9219ABCPZ-65 | 功能描述:IC ADC 10BIT SRL 65MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 其它有关文件:TSA1204 View All Specifications 标准包装:1 系列:- 位数:12 采样率(每秒):20M 数据接口:并联 转换器数目:2 功率耗散(最大):155mW 电压电源:模拟和数字 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-TQFP 供应商设备封装:48-TQFP(7x7) 包装:Digi-Reel® 输入数目和类型:4 个单端,单极;2 个差分,单极 产品目录页面:1156 (CN2011-ZH PDF) 其它名称:497-5435-6 |

| AD9219ABCPZRL7-40 | 功能描述:IC ADC 10BIT SRL 40MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD9219ABCPZRL7-65 | 功能描述:IC ADC 10BIT SRL 65MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| AD9219BCPZ-40 | 制造商:Analog Devices 功能描述:ADC Quad Pipelined 40Msps 10-bit Serial 48-Pin LFCSP EP 制造商:Analog Devices 功能描述:IC 10BIT ADC QUAD 40MSPS LFCSP48 |

| AD9219BCPZ-65 | 制造商:Analog Devices 功能描述:ADC Quad Pipelined 65Msps 10-bit Serial 48-Pin LFCSP EP 制造商:Analog Devices 功能描述:IC 10BIT ADC QUAD 65MSPS LFCSP48 |

发布紧急采购,3分钟左右您将得到回复。