- 您现在的位置:买卖IC网 > PDF目录10512 > AD9222ABCPZ-65 (Analog Devices Inc)IC ADC 12BIT SRL 65MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9222ABCPZ-65 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 20/60页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT SRL 65MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 65M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 8 |

| 功率耗散(最大): | 950.5mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 16 个单端,单极;8 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

Data Sheet

AD9222

Rev. F | Page 27 of 60

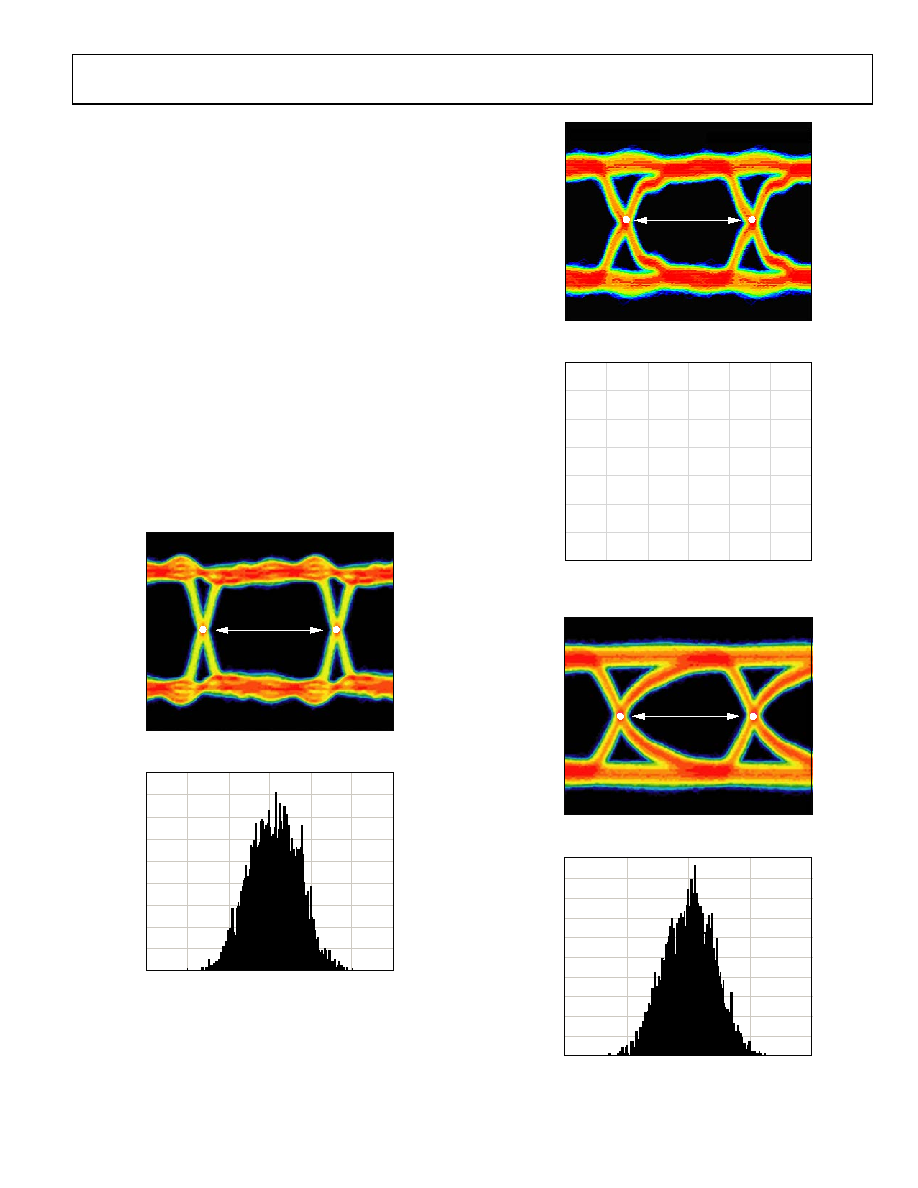

An example of the LVDS output using the ANSI-644 standard

(default) data eye and a time interval error (TIE) jitter histogram

with trace lengths less than 24 inches on standard FR-4 material is

examples of trace lengths exceeding 24 inches on standard FR-4

material. Notice that the TIE jitter histogram reflects the decrease

of the data eye opening as the edge deviates from the ideal position.

It is the user’s responsibility to determine if the waveforms meet

the timing budget of the design when the trace lengths exceed

24 inches. Additional SPI options allow the user to further increase

the internal termination (increasing the current) of all eight outputs

in order to drive longer trace lengths (see Figure 77 and Figure 78).

Even though this produces sharper rise and fall times on the data

edges and is less prone to bit errors, the power dissipation of the

DRVDD supply increases when this option is used.

In cases that require increased driver strength to the DCO± and

FCO± outputs because of load mismatch, Register 0x15 allows

the user to increase the drive strength by 2×. To do this, set the

appropriate bit in Register 0x5. Note that this feature cannot be

used with Bit 4 and Bit 5 in Register 0x15. Bit 4 and Bit 5 take

precedence over this feature. See the Memory Map section for

more details.

500

400

300

200

100

–500

–400

–300

–200

–100

0

–1.0ns

–1.5ns

–0.5ns

0ns

0.5ns

1.0ns

1.5ns

EYE

D

IA

G

R

A

M

VO

L

T

A

G

E

(m

V)

EYE: ALL BITS

ULS: 12071/12071

90

50

10

20

30

40

60

70

80

0

–150ps

–100ps

–50ps

0ps

50ps

100ps

150ps

TIE

J

ITTE

R

H

IS

TOGR

A

M

(

H

it

s

)

05967-

061

Figure 73. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths

Less than 24 Inches on Standard FR-4, AD9222-50

600

400

200

–600

–400

–200

0

–1.0ns

–1.5ns

–0.5ns

0ns

0.5ns

1.0ns

1.5ns

EYE

D

IA

G

R

A

M

VO

L

T

A

G

E

(m

V)

EYE: ALL BITS

ULS: 9596/15596

20

40

60

80

100

140

120

0

–150ps

–100ps

–50ps

0ps

50ps

100ps

150ps

TIE

J

ITTE

R

H

IS

TOGR

A

M

(

H

it

s

)

05967-

106

Figure 74. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths

Less than 24 Inches on Standard FR-4, AD9222-65

60

80

90

70

50

40

20

10

100

30

0

–200ps

–100ps

100ps

0ps

200ps

TIE

J

ITTE

R

H

IS

TOGR

A

M

(

H

it

s

)

500

400

300

200

100

–500

–400

–300

–200

–100

0

–1.0ns

–0.5ns

0ns

0.5ns

1.5ns

–1.5ns

1.0ns

EYE

D

IA

G

R

A

M

VO

L

T

A

G

E

(m

V)

EYE: ALL BITS

ULS: 12067/12067

05967-

059

Figure 75. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths

Greater than 24 Inches on Standard FR-4, AD9222-50

相关PDF资料 |

PDF描述 |

|---|---|

| MS3102E28-3S | CONN RCPT 3POS BOX MNT W/SCKT |

| LTC2220CUP-1#PBF | IC ADC 12BIT 185MSPS 64-QFN |

| MS3102E32-17PX | CONN RCPT 4POS BOX MNT W/PINS |

| UP050CH120J-B-B | CAP CER 12PF 50V 5% AXIAL |

| VE-BTY-MV | CONVERTER MOD DC/DC 3.3V 99W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9222ABCPZRL7-40 | 制造商:Analog Devices 功能描述:ADC OCTAL PIPELINED 40MSPS 12-BIT SERL 64LFCSP EP - Tape and Reel |

| AD9222ABCPZRL7-50 | 功能描述:IC ADC 12BIT SRL 50MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9222ABCPZRL7-65 | 功能描述:IC ADC 12BIT SRL 65MSPS 64LFCSP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| AD9222BCPZ-40 | 制造商:Analog Devices 功能描述:Octal ADC Pipelined 40Msps 12-bit Serial 64-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述: |

| AD9222BCPZ-50 | 制造商:Analog Devices 功能描述:ADC Octal Pipelined 50Msps 12-bit Serial 64-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:12BIT ADC OCTAL 50MSPS LFCSP-64 |

发布紧急采购,3分钟左右您将得到回复。