- 您现在的位置:买卖IC网 > PDF目录16534 > AD9514/PCBZ (Analog Devices Inc)BOARD EVAL CLOCK 3CH AD9514 PDF资料下载

参数资料

| 型号: | AD9514/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/28页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL CLOCK 3CH AD9514 |

| 设计资源: | AD9513/14/15 Eval Brd Schematics AD9513/14/15 Gerber Files AD9514 Eval Brd BOM |

| 标准包装: | 1 |

| 主要目的: | 计时,时钟分配 |

| 已用 IC / 零件: | AD9514 |

| 已供物品: | 板 |

| 相关产品: | AD9514BCPZ-ND - IC CLOCK DIST 3OUT PLL 32LFCSP AD9514BCPZ-REEL7-ND - IC CLOCK DIST 3OUT PLL 32LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

AD9514

Rev. 0 | Page 19 of 28

Synchronization is initiated by pulling the SYNCB pin low for a

minimum of 5 ns. The input clock does not have to be present

at the time the command is issued. The synchronization occurs

after four input clock cycles.

The synchronization applies to clock outputs:

that are not turned OFF

where the divider is not divide = 1 (divider bypassed)

An output with its divider set to divide = 1 (divider bypassed) is

always synchronized with the input clock, with a propagation

delay.

The SYNCB pin must be pulled up for normal operation. Do

not let the SYNCB pin float.

RSET RESISTOR

The internal bias currents of the AD9514 are set by the

RSET resistor. This resistor should be as close as possible to

the value given as a condition in the Specifications section

(RSET = 4.12 kΩ). This is a standard 1% resistor value and

should be readily obtainable. The bias currents set by this

resistor determine the logic levels and operating conditions

of the internal blocks of the AD9514. The performance figures

given in the Specifications section assume that this resistor

value is used for RSET.

VREF

The VREF pin provides a voltage level of VS. This voltage is

one of the four logic levels used by the setup pins (S0 to S10).

These pins set the operation of the AD9514. The VREF pin

provides sufficient drive capability to drive as many of the setup

pins as necessary, up to all on a single part. The VREF pin

should be used for no other purpose.

SETUP CONFIGURATION

The specific operation of the AD9514 is set by the logic levels

applied to the setup pins (S0 to S10). These pins use four-state

logic. The logic levels used are VS and GND, plus VS and

VS. The VS level is provided by the internal self-biasing on

each of the setup pins (S0 to S10). This is the level seen by a

setup pin that is left not connected (NC). The VS level is

provided by the VREF pin. All setup pins requiring the VS

level must be tied to the VREF pin.

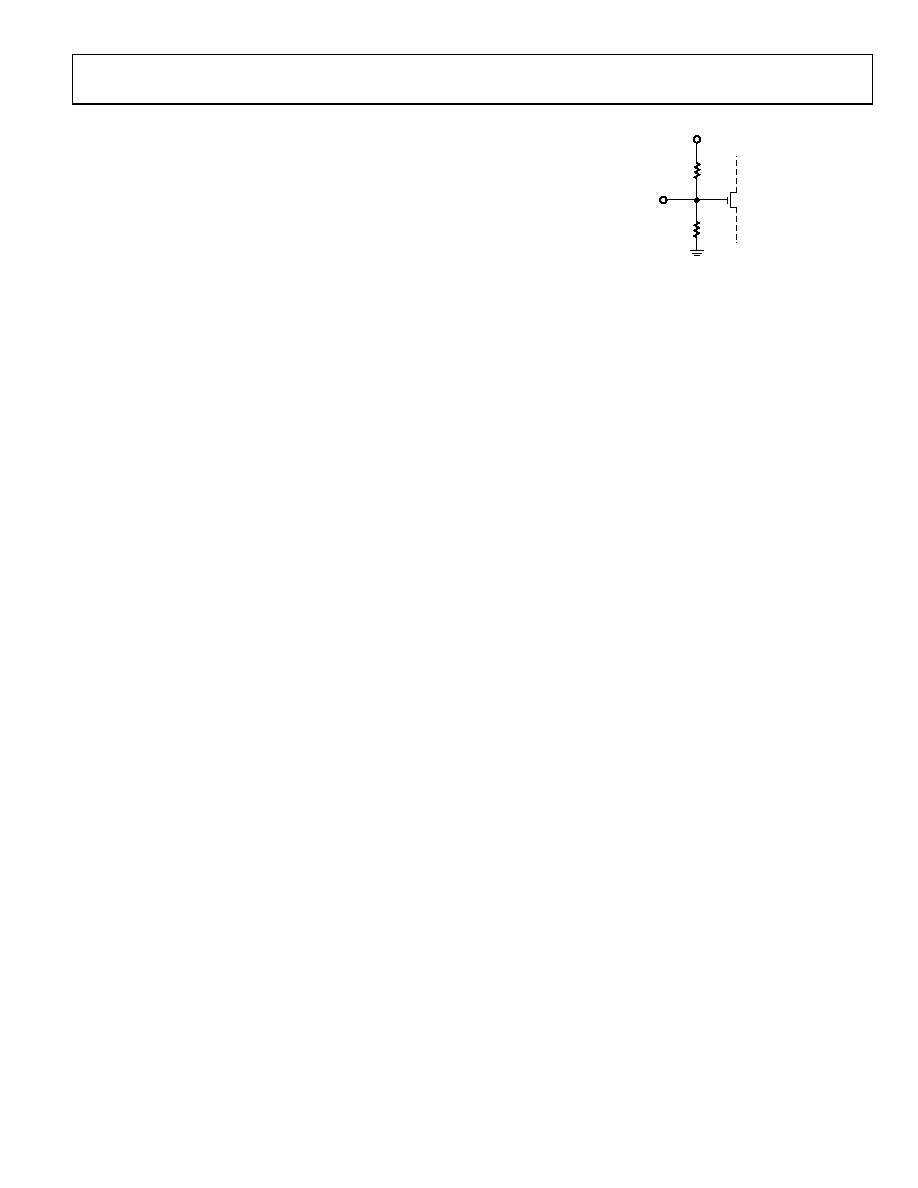

SETUP PIN

S0 TO S10

60k

Ω

30k

Ω

VS

05596-

023

Figure 28. Setup Pin (S0 to S10) Equivalent Circuit

The AD9514 operation is determined by the combination of

logic levels present at the setup pins. The setup configurations

logic levels are referred to as 0, , , and 1. These numbers

represent the fraction of the VS voltage that defines the logic

levels. See the setup pins thresholds in Table 6.

The meaning of some of the setup pins depends on the logic

level set on other pins. For example, the effect of the S3 to S4

pair of pins depends on whether S0 = 0. If S0 = 0, the delay

block for OUT2 is off, and the logic levels on S3 to S4 set the

phase word of the OUT2 divider. However, if S0 ≠ 0, then the

full-scale delay for OUT2 is set by the logic level on S0, and S3

to S4 sets the delay block fine adjust (fraction of full scale).

S1 and S2 together determine the logic level of each output or

whether a channel is off. An output that is set to OFF is

powered down, including the divider.

OUT0 and OUT1 are LVPECL. The LVPECL output differential

voltage (VOD) can have three possible levels: 410 mV, 790 mV,

and 960 mV (limited to the available combinations, see Table 11).

OUT2 can be set to either LVDS or CMOS levels.

S5 and S6 effect depends on S2. If S2 = 0 (OUT2 is off), S5 and

S6 set the OUT1 phase word. If S2 ≠ 0, S5 and S6 set the OUT2

divide ratio. If S2 = , then the value in S9 and S10 overrides

the divide ratio for OUT2.

S7 and S8 depend on S2 and S0. If S2 ≠ 1, these pins set the

OUT1 divide ratio. However, if S2 = 1 (OUT1 is off) and S0 ≠ 0,

S7 and S8 set the phase word for OUT2.

S9 and S10 depend on S2. If S2 ≠ , these pins set the OUT0

divide ratio. If S2 = , they set the OUT2 divide ratio,

overriding S5 and S6.

相关PDF资料 |

PDF描述 |

|---|---|

| EEU-EB2V220 | CAP ALUM 22UF 350V 20% RADIAL |

| ADCLK925/PCBZ | BOARD EVAL FOR ADCLK925 16LFCSP |

| MCP131T-195I/TT | IC SUPERVISOR 1.95V LOW SOT-23B |

| VE-J0Z-EZ-S | CONVERTER MOD DC/DC 2V 10W |

| H3CKH-4018M | IDC CABLE - HKC40H/AE40M/HPK40H |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9515 | 制造商:AD 制造商全称:Analog Devices 功能描述:1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Two Outputs |

| ad9515/pcb | 制造商:Analog Devices 功能描述:EVAL KIT FOR 1.6 GHZ CLOCK DISTRIBUTION IC, DIVIDERS, DLY AD - Bulk |

| AD9515/PCBZ | 功能描述:BOARD EVAL CLOCK 2CH AD9515 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9515BCPZ | 功能描述:IC CLOCK DIST 2OUT PLL 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| AD9515BCPZ-REEL7 | 功能描述:IC CLOCK DIST 2OUT PLL 32LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

发布紧急采购,3分钟左右您将得到回复。