- 您现在的位置:买卖IC网 > PDF目录1987 > AD9523-1BCPZ-REEL7 (Analog Devices Inc)IC INTEGER-N CLCK GEN 72LFCSP PDF资料下载

参数资料

| 型号: | AD9523-1BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/60页 |

| 文件大小: | 0K |

| 描述: | IC INTEGER-N CLCK GEN 72LFCSP |

| 标准包装: | 400 |

| 类型: | 时钟/频率发生器,扇出缓冲器(分配),多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,光纤通道,SONET/SDH |

| 输入: | CMOS |

| 输出: | HSTL,LVCMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:14 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1GHz |

| 电源电压: | 1.768 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 72-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 72-LFCSP |

| 包装: | 带卷 (TR) |

| 配用: | AD9523/PCBZ-ND - BOARD EVAL FOR AD9523 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

AD9523-1

Rev. B | Page 24 of 60

Input 2× Frequency Multiplier

The 2× frequency multiplier provides the option to double the

frequency at the PLL2 input. This allows the user to take advantage

of a higher frequency at the input to the PLL (PFD) and, thus,

allows for reduced in-band phase noise and greater separation

between the frequency generated by the PLL and the modulation

spur associated with PFD. However, increased reference spur

separation results in harmonic spurs, introduced by the frequency

multiplier, that increase as the duty cycle deviates from 50% at the

OSC_IN inputs. As such, beneficial use of the frequency multiplier

is application-specific. Typically, a VCXO with proper interfacing

has a duty cycle that is approximately 50% at the OSC_IN inputs.

Note that the maximum output frequency of the 2× frequency

multipliers must not exceed the maximum PFD rate that is

specified in Table 11.

PLL2 Feedback Divider

PLL2 has a feedback divider (N divider) that enables it to provide

integer frequency up-conversion. The PLL2 N divider is a com-

bination of a prescaler (P) and two counters, A and B.

The total

divider value is

N = (P × B) + A

where P = 4.

The feedback divider is a dual modulus prescaler architecture, with

a nonprogrammable P that is equal to 4. The value of the B counter

can be from 3 to 63, and the value of the A counter can be from 0 to 3.

However, due to the architecture of the divider, there are constraints,

as listed in

PLL2 Loop Filter

The PLL2 loop filter requires the connection of an external

capacitor from LF2_EXT_CAP (Pin 11) to LDO_VCO (Pin 12),

as illustrated in Figure 27. The value of the external capacitor

depends on the operating mode and the desired phase noise

performance. For example, a loop bandwidth of approximately

500 kHz produces the lowest integrated jitter. A lower bandwidth

produces lower phase noise at 1 MHz but increases the total

integrated jitter.

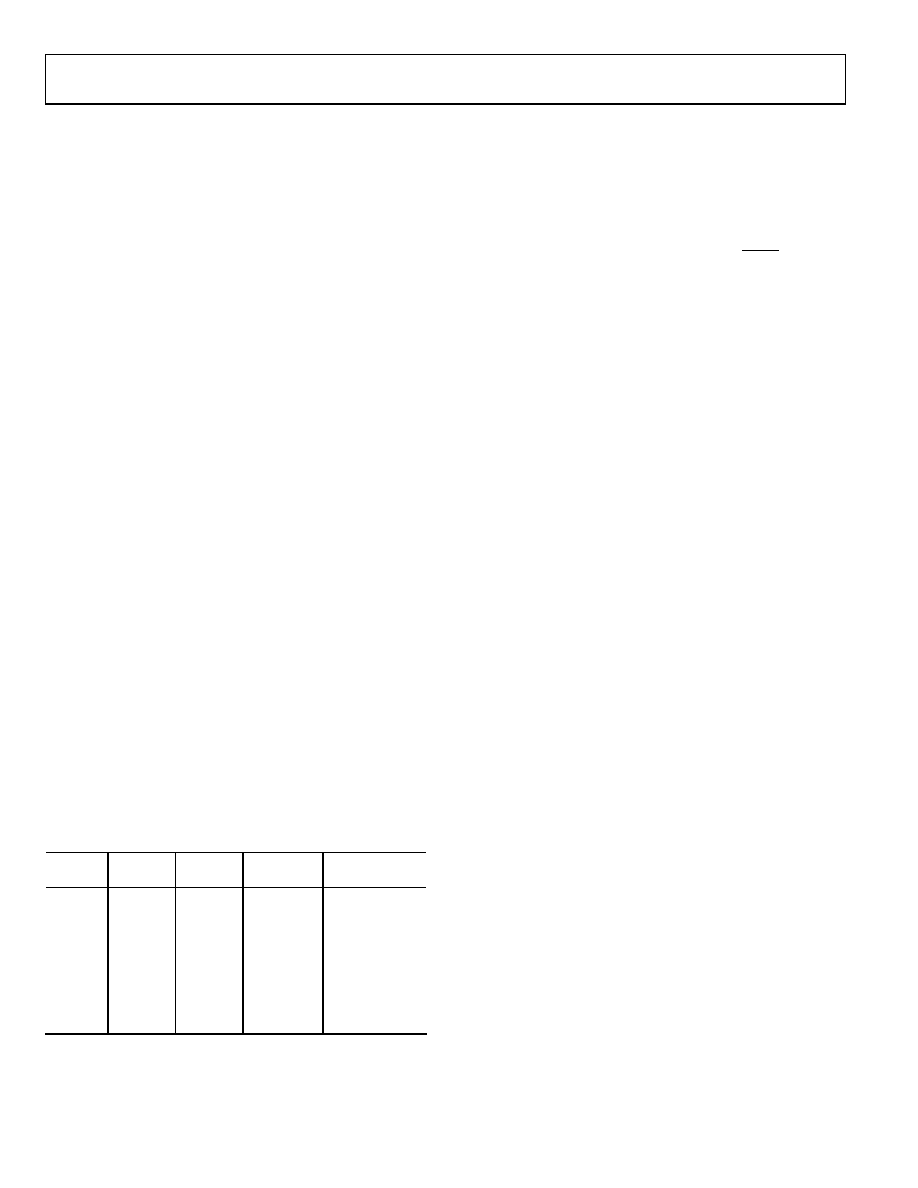

Table 20. PLL2 Loop Filter Programmable Values

RZERO

(Ω)

CPOLE1

(pF)

RPOLE2

(Ω)

CPOLE2

(pF)

(pF)

3250

48

900

Fixed at 16

Typical at 1000

3000

40

450

2750

32

300

2500

24

225

2250

16

2100

8

2000

0

1850

1 External loop filter capacitor.

VCO Divider M1 and VCO Divider M2

The VCO dividers provide frequency division between the internal

VCO and the clock distribution. Each VCO divider can be set to

divide by 3, 4, or 5. When the AD9523-1 is used without any

zero delay feedback (internal or external), the phase relationship

between the reference inputs and the outputs is a function of

the phase relationship between the OSC input and the reference

inputs. Because the VCO divider is not reset by SYNC, there is

an additional phase variability of up to x VCO periods, where

x = VCO divider setting.

VCO Calibration

The AD9523-1 on-chip VCO must be manually calibrated to

ensure proper operation over process and temperature. This is

accomplished by setting the calibrate VCO bit (Register 0x0F3,

Bit 1) to 1. (This bit is not self-clearing.) The setting can be

performed as part of the initial setup before executing the

IO_Update bit (Register 0x234, Bit 0 = 1). A readback bit, VCO

calibration in progress (Register 0x22D, Bit 0), indicates when

a VCO calibration is in progress by returning a logic true (that is,

Bit 0 = 1). If the EEPROM is in use, setting the calibrate VCO bit

to 1 before saving the register settings to the EEPROM ensures

that the VCO calibrates automatically after the EEPROM has

loaded. After calibration, it is recommended that a sync be initiated

(see the Clock Distribution Synchronization section).

Note that the calibrate VCO bit defaults to 0. This bit must

change from 0 to 1 to initiate a calibration sequence. Therefore,

any subsequent calibrations require the following sequence:

1.

Register 0x0F3, Bit 1 (calibrate VCO bit) = 0

2.

Register 0x234, Bit 0 (IO_Update bit) = 1

3.

Register 0x0F3, Bit 1 (calibrate VCO bit) = 1

4.

Register 0x234, Bit 0 (IO_Update bit) = 1

VCO calibration is controlled by a calibration controller that

runs off the VCXO input clock. The calibration requires that

PLL2 be set up properly to lock the PLL2 loop and that the

VCXO clock be present.

During power-up or reset, the distribution section is automatically

held in sync until the first VCO calibration is finished. Therefore,

no outputs can occur until VCO calibration is complete and PLL2

is locked.

Initiate a VCO calibration under the following conditions:

After changing any of the PLL2 B counter and A counter

settings or after a change in the PLL2 reference clock

frequency. This means that a VCO calibration should be

initiated any time that a PLL2 register or reference clock

changes such that a different VCO frequency is the result.

Whenever system calibration is desired. The VCO is designed

to operate properly over extremes of temperature even

when it is first calibrated at the opposite extreme. However,

a VCO calibration can be initiated at any time, if desired.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9523BCPZ | IC INTEGER-N CLCK GEN 72LFCSP |

| AD9524BCPZ | IC INTEGER-N CLCK GEN 48LFCSP |

| AD9540BCPZ-REEL7 | IC CLOCK GEN/SYNTHESIZER 48LFCSP |

| AD9547BCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| AD9548BCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 88LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9523BCPZ | 功能描述:IC INTEGER-N CLCK GEN 72LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD9523BCPZ-REEL7 | 功能描述:IC INTEGER-N CLCK GEN 72LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| AD9524 | 制造商:AD 制造商全称:Analog Devices 功能描述:Jitter Cleaner and Clock Generator with 6 Differential or 13 LVCMOS Outputs |

| AD9524/PCBZ | 功能描述:BOARD EVAL FOR AD9524 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9524BCPZ | 功能描述:IC INTEGER-N CLCK GEN 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。