- 您现在的位置:买卖IC网 > PDF目录9093 > AD9572ACPZPEC-R7 (Analog Devices Inc)IC PLL CLOCK GEN 25MHZ 40LFCSP PDF资料下载

参数资料

| 型号: | AD9572ACPZPEC-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 16/20页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLOCK GEN 25MHZ 40LFCSP |

| 标准包装: | 750 |

| 类型: | 时钟发生器,扇出配送,多路复用器 |

| PLL: | 是 |

| 输入: | 晶体 |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:7 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 156.25MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 2.97 V ~ 3.63 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-WQ(6x6) |

| 包装: | 带卷 (TR) |

AD9572

Rev. B | Page 5 of 20

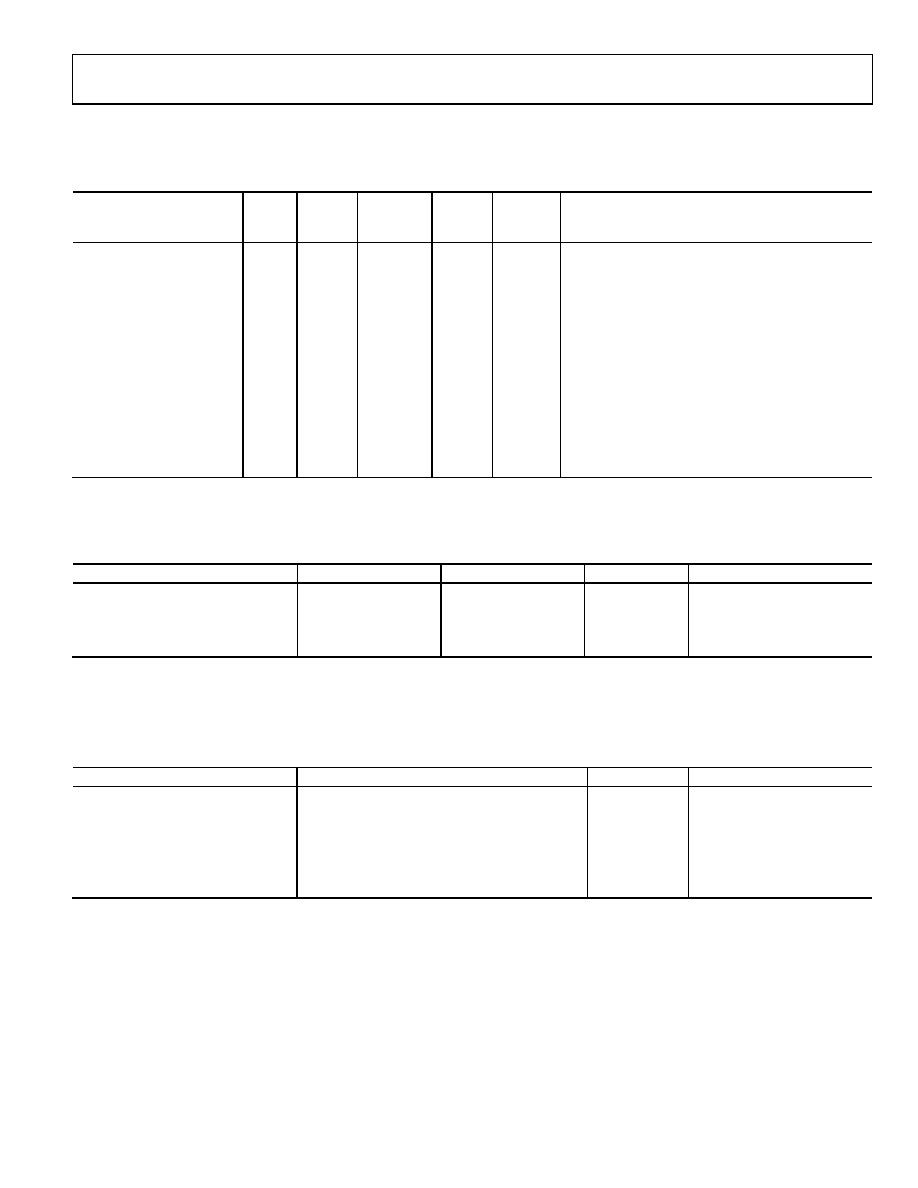

LVPECL CLOCK OUTPUT JITTER

Typical (typ) is given for VS = 3.3 V, TA = 25°C, unless otherwise noted.

Table 3.

Jitter Integration

Bandwidth (Typ)

100

MHz

106.25

MHz

125 MHz

33M =

Off/On

156.25

MHz

Unit

Test Conditions/Comments

12 kHz to 20 MHz (Typ)

0.61

0.45

0.44/2.2

0.46

ps rms

LVPECL output frequency combinations are 1 × 156.25

MHz, 1 × 100 MHz, 1 × 125 MHz, 2 × 106.25 MHz

12 kHz to 20 MHz (Max)

0.87

0.81

0.56 (off

only)

0.56

ps rms

LVPECL output frequency combinations are 1 × 156.25

MHz, 1 × 100 MHz, 1 × 125 MHz, 2 × 106.25 MHz

1.875 MHz to 20 MHz (Typ)

0.28

ps rms

LVPECL output frequency combinations are 1 × 156.25

MHz, 1 × 100 MHz, 1 × 125 MHz, 2 × 106.25 MHz

637 kHz to 10 MHz (Typ)

0.23

ps rms

LVPECL output frequency combinations are 1 × 156.25

MHz, 1 × 100 MHz, 1 × 125 MHz, 2 × 106.25 MHz

200 kHz to 10 MHz (Typ)

0.38

0.24/2.2

ps rms

LVPECL output frequency combinations are 1 × 156.25

MHz, 1 × 100 MHz, 1 × 125 MHz, 2 × 106.25 MHz

12 kHz to 35 MHz (Typ)

0.52 (off

only)

ps rms

LVPECL output frequency combinations are 156.25

MHz unterminated, 2 × 125 MHz, 2 × 106.25 MHz

12 kHz to 35 MHz (Max)

0.66 (off

only)

ps rms

LVPECL output frequency combinations are 156.25

MHz unterminated, 2 × 125 MHz, 2 × 106.25 MHz

CMOS CLOCK OUTPUT JITTER

Typical (typ) is given for VS = 3.3 V, TA = 25°C, unless otherwise noted.

Table 4.

Jitter Integration Bandwidth

25 MHz

33.3 MHz

Unit

Test Conditions/Comments

12 kHz to 5 MHz (Typ)

0.78

0.41

ps rms

12 kHz to 5 MHz (Max)

1.1

N/A

ps rms

200 kHz to 5 MHz (Typ)

0.76

0.52

ps rms

200 kHz to 5 MHz (Max)

1.0

N/A

ps rms

REFERENCE INPUT

Typical (typ) is given for VS = 3.3 V ± 10%, TA = 25°C, unless otherwise noted. Minimum (min) and maximum (max) values are given

over full VS and TA (40°C to +85°C) variation.

Table 5.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

CLOCK INPUT (REFCLK)

Input Frequency

25

MHz

Input High Voltage

2.0

V

Input Low Voltage

0.8

V

Input Current

1.0

+1.0

μA

Input Capacitance

2

pF

相关PDF资料 |

PDF描述 |

|---|---|

| X9410WS24IT1 | IC XDCP DUAL 64-TAP 10K 24-SOIC |

| VI-252-MW-S | CONVERTER MOD DC/DC 15V 100W |

| MS27496E9B98S | CONN RCPT 3POS BOX MNT W/SCKT |

| X9410WS24I-2.7T1 | IC XDCP DUAL 64-TAP 10K 24-SOIC |

| M83723/73R2461N | CONN RCPT 61POS JAM NUT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9572ACPZPEC-RL | 功能描述:IC PLL CLOCK GEN 25MHZ 40LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| AD9572-EVALZ-LVD | 制造商:AD 制造商全称:Analog Devices 功能描述:Fiber Channel/Ethernet Clock Generator IC, PLL Core, Dividers, 7 Clock Outputs |

| AD9572-EVALZ-PEC | 制造商:AD 制造商全称:Analog Devices 功能描述:Fiber Channel/Ethernet Clock Generator IC, PLL Core, Dividers, 7 Clock Outputs |

| AD9572XCPZLVD | 制造商:Analog Devices 功能描述: |

| AD9572XCPZPEC | 制造商:Analog Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。