参数资料

| 型号: | AD9785BSVZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 36/64页 |

| 文件大小: | 0K |

| 描述: | IC DAC 12BIT 800MSPS 100TQFP |

| 产品培训模块: | Data Converter Fundamentals DAC Architectures |

| 标准包装: | 1 |

| 系列: | TxDAC® |

| 位数: | 12 |

| 数据接口: | 串行 |

| 转换器数目: | 2 |

| 电压电源: | 模拟和数字 |

| 功率耗散(最大): | 450mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP 裸露焊盘 |

| 供应商设备封装: | 100-TQFP-EP(14x14) |

| 包装: | 托盘 |

| 输出数目和类型: | 2 电流,单极;2 电流,双极 |

| 采样率(每秒): | 800M |

| 产品目录页面: | 785 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页当前第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

AD9785/AD9787/AD9788

Rev. A | Page 41 of 64

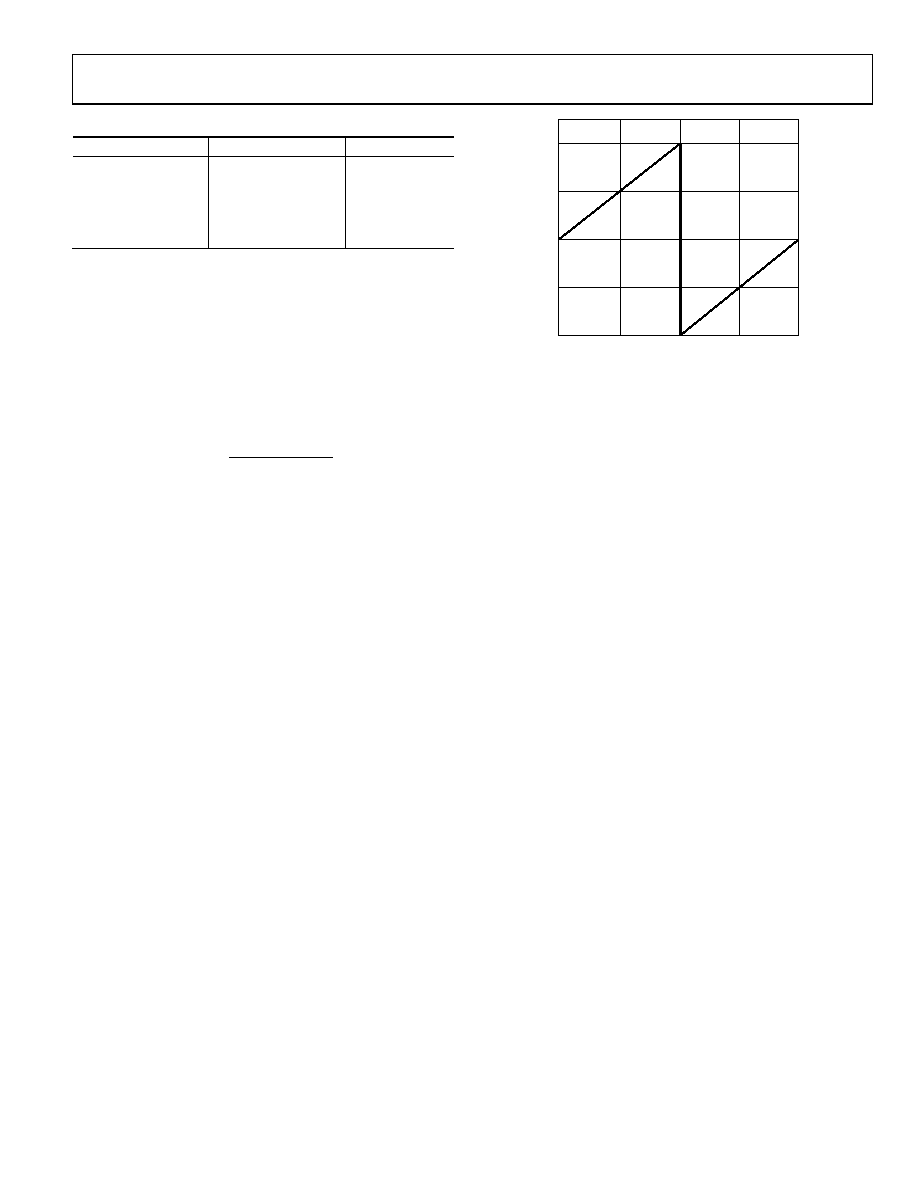

Table 31. Inverse Sinc Filter

Lower Coefficient

Upper Coefficient

Integer Value

H(1)

H(9)

+2

H(2)

H(8)

4

H(3)

H(7)

+10

H(4)

H(6)

35

H(5)

–

+401

The inverse sinc filter is disabled by default. It can be enabled by

setting the inverse sinc enable bit (Bit 9) in Register 0x01.

DIGITAL AMPLITUDE AND OFFSET CONTROL

The gain of the I datapath and the Q datapath can be independ-

ently scaled by adjusting the I DAC Amplitude Scale Factor [8:0]

or Q DAC Amplitude Scale Factor [8:0] value in Register 0x0C.

These values control the input to a digital multiplier. The value

of the scale factor ranges from 0 to 3.9921875 and can be

calculated as follows:

128

]

0

:

8

[

Factor

Scale

Value

Factor

Scale

The digital scale factor can be used to compensate for amplitude

imbalance between the I and Q channels or to provide equal

gain scaling to both channels for output level adjustment. Note

that when the gain is set to 1.0 (scale factor = 0x80), the gain

block is bypassed. When bypassed, the gain block has a different

delay from when it is used. Therefore, to maintain matched

latency in each path, both gain blocks should be set to exactly

1.0, or neither path should be set to exactly 1.0. Failing to

maintain matched latencies in the I and Q paths creates a phase

imbalance in quadrature signals, which results in poor sideband

suppression of upconverted signals.

The dc value of the I datapath and the Q datapath can also be

independently controlled. This is accomplished by adjusting

the I DAC Offset [15:0] and Q DAC Offset [15:0] values in

Register 0x0D. These values are added directly to the datapath

values. Care should be taken not to overrange the transmitted

values.

Figure 59 shows how the DAC offset current varies as a function

of the I DAC Offset [15:0] and Q DAC Offset [15:0] values. With

the digital inputs fixed at midscale (0x0000, twos complement

data format), the figure shows the nominal IOUTx_P and IOUTx_N

currents as the DAC offset value is swept from 0 to 65535.

Because IOUTx_P and IOUTx_N are complementary current outputs,

the sum of IOUTx_P and IOUTx_N is always 20 mA.

0x0000

0x4000

0x8000

0xC000

0xFFFF

5

10

15

20

5

10

15

20

0

DAC OFFSET VALUE

I O

U

T

x_N

(m

A

)

I O

U

T

x_P

(m

A

)

07

09

8-

10

8

Figure 59. DAC Output Currents vs. DAC Offset Value

The offset currents generated by the DAC offset parameter

increase from 0 mA to 10 mA as the offset is swept from 0 to

0x7FFF. The offset currents increase from 10 mA to 0 mA as

the offset is swept from 0x8000 to 0xFFFF.

DIGITAL PHASE CORRECTION

The purpose of the phase correction block is to enable compens-

ation of the phase imbalance of the analog quadrature modulator

following the DAC. If the quadrature modulator has a phase

imbalance, the unwanted sideband appears with significant

energy. Adjusting the phase correction word can optimize image

rejection in single sideband radios.

Ordinarily the I and Q channels have an angle of precisely 90°

between them. The Phase Correction Word [9:0] (Register 0x0B)

is used to change the angle between the I and Q channels. When

the Phase Correction Word [9:0] is set to 1000000000b, the

Q DAC output moves approximately 14° away from the I DAC

output, creating an angle of 104° between the channels. When

the Phase Correction Word [9:0] is set to 0111111111b, the

Q DAC output moves approximately 14° towards the I DAC

output, creating an angle of 76° between the channels. Based on

these two endpoints, the resolution of the phase compensation

register is approximately 28°/1024 or 0.027° per code.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27473E12F3PLC | CONN HSG PLUG 3POS STRGHT PINS |

| VE-J4Z-MZ-S | CONVERTER MOD DC/DC 2V 10W |

| MS27474E24A1S | CONN RCPT 128POS JAM NUT W/SCKT |

| MS27484T10B35B | CONN HSG PLUG 13POS STRGHT SCKT |

| VE-J4Y-MZ-S | CONVERTER MOD DC/DC 3.3V 16.5W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9785BSVZRL | 功能描述:IC DAC 12BIT 800MSPS 100TQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:TxDAC® 产品培训模块:Data Converter Fundamentals DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k |

| AD9785-DPG2-EBZ | 功能描述:BOARD EVALUATION FOR AD9785 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:TxDAC® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| AD9785-EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD9785 制造商:Analog Devices 功能描述:DUAL 12B, 1GSPS D-A CONVERTER - Bulk 制造商:Analog Devices 功能描述:Digital to Analog Eval. Board |

| AD9786 | 制造商:AD 制造商全称:Analog Devices 功能描述:16-Bit, 200 MSPS/500 MSPS TxDAC+ with 2】/4】/8】 Interpolation and Signal Processing |

| AD9786BSV | 制造商:Analog Devices 功能描述:DAC 1-CH Interpolation Filter 16-bit 80-Pin TQFP EP 制造商:Analog Devices 功能描述:IC 16BIT DAC SMD 9786 TQFP80 |

发布紧急采购,3分钟左右您将得到回复。